Die Open Verification Library (OVL) ist eine Bibliothek von Property Checkern für digitale Schaltkreisbeschreibungen, die in gängigen Hardware Description Languages geschrieben sind und von Accelera gepflegt werden. Die OVL Checker können nicht nur in der dynamischen Simulation, sondern auch in der formalen Verifikation und Emulation eingesetzt werden. Außerdem bietet die OVL-basierte Verifikationstechnologie den Entwicklern die einfachste Möglichkeit, eine Assertion-basierte Verifikation ihres Designs zu implementieren. Schließlich unterstützt OVL jede HDL-Sprache (Verilog, SystemVerilog, VHDL) und ermöglicht so eine Assertion-basierte Verifikation mit jedem Simulationswerkzeug.

In diesem Webinar werden wir praktische Anleitungen für den Einsatz der Open Verification Library (OVL) im Design- und Verifikationsprozess vorstellen. Anhand verschiedener Codebeispiele wird gezeigt, wie OVL effizient für die Verifikation von Verilog- und VHDL-Designs eingesetzt werden kann. Statische, formale und emulationsbasierte Verifikationsmethoden, die OVL verwenden, werden ebenfalls vorgestellt.

Agenda:

- Assertion-basierte Verifikation: Ein Überblick

- Einführung in die Assertion-Based Verification mit OVL

- Anwendung der OVL-basierten Verifikation auf HDL-Designs

- Verwendung von OVL-Checkern bei Emulation/Prototyping

- Formale Modellprüfung mit OVL

- Live-Demo

eVision Systems GmbH kündigt neuartigen PCIeGen3 und 4 Protokoll-Analysator von Prodigy Technovations an

PGY-PCIeGen3/4-PA PCIe Protocol AnalyzerForstinning (Deutschland), 09. Oktober 2022 - eVision Systems GmbH, autorisierter Distributor von Prodigy Technovations für Zentraleuropa, kündigt den PGY-PCIeGen3/4-PA PCIe Protocol Analyzer an, der 2.5, 5.0. 8.0 und 16GT/S...

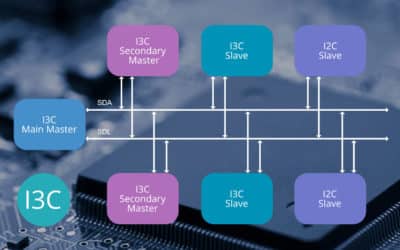

Die 10 größten Probleme bei der Entwicklung mit den I3C Bussystem

Entwickler von Endgeräten und embedded Systeme, speziell für den Einsatz im IoT (Internet of Things), Automotive Bereich und Industrieautomatisierung, sind mit immer höheren Anforderungen an niedrigen Stromverbrauch, Datenbandbreite und Miniaturisierung konfrontiert....

Was ist ein Logikanalysator / Logic analyzer?

Ein Logik-Analysator ist ein elektronisches Messgerät, das mehrere Signale aus einem digitalen Design erfasst und anzeigt. Es ist ein ausgezeichnetes Werkzeug zur Überprüfung und Fehlersuche bei IC`s, digitalen Systemen und digitalen Schaltungen wie z.B. bei embedded...

Riviera-PRO unterstützt OpenCPI für heterogenes Embedded Computing

Aldec unterstützt mit der neuesten Version von Riviera-PRO (Version 2022.04) die Open Component Portability Infrastructure (OpenCPI).

Agnisys kündigt Qualifizierung nach ISO 26262 und IEC 61508 für den gesamten Automatisierungsprozess in der SoC-Spezifikation an

Entwickler von sicherheitsrelevante elektrische/elektronische Systeme in Kraftfahrzeugen können nun die Agnisys Lösungen ohne zusätzliche Tool-Qualifizierung einsetzen

FPGA Verifizierung Code- Funktions- und Spezifikationsabdeckung

Functional Coverage wird oft zusammen mit der FPGA Verifikation nach dem Zufallsprinzip erwähnt, und das ist eine großartige Kombination.