Statische Verifikation

Beim Erstellen des VHDL Codes können sich eine Menge Fehler einschleichen. Das können einfache Tippfehler, Syntaxfehler, semantische Fehler oder auch strukturelle Fehler sein.

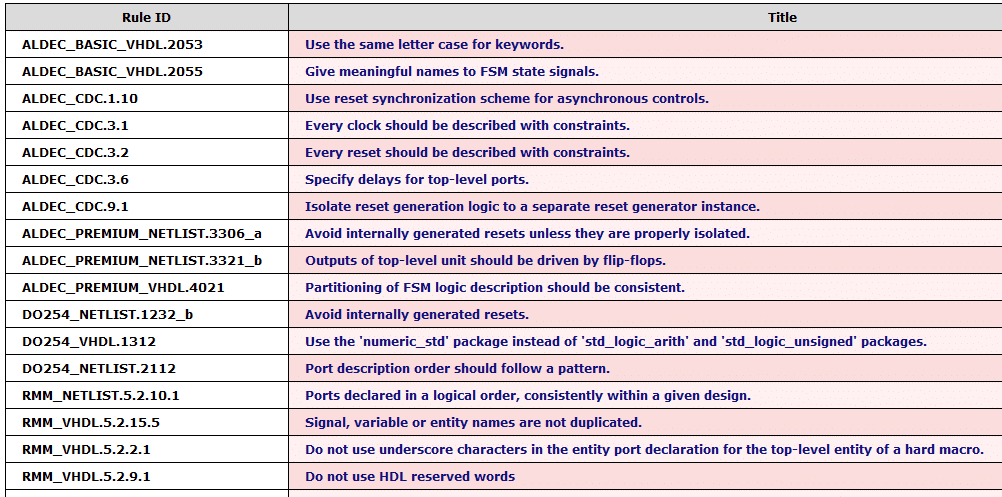

Speziell Fehler, die nicht während der Kompilation eines einzigen Files erkennbar sind, können in der Regel nicht durch den Editor alleine erkannt werden. Um solche Probleme rechtzeitig zu erkennen können Linting Tools eingesetzt werden. Diese ermöglichen auch das Einhalten von speziell definierten Designregeln. Mit Alint-Pro bietet ALDEC ein Linting Werkzeug an, für das nicht nur verschiedene Regelsätze zur Verfügung steht, sondern das auch fileübergreifende Überprüfungen wie CDC Checks (Clock Domain Crossing) ermöglicht.