Statische Design-Verifikation

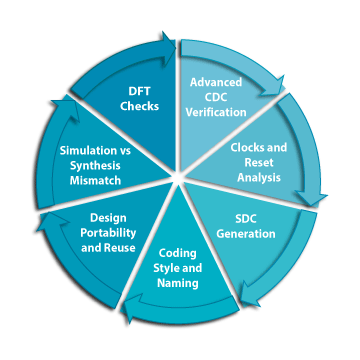

ALINT-PRO™ ist eine Design-Verifikationslösung für RTL-Code, der in VHDL, Verilog und SystemVerilog geschrieben wurde. Sie konzentriert sich auf die Verifizierung von Codierungsstil und Namenskonventionen, RTL- und Post-Synthese-Simulationsfehlern, reibungsloser und optimaler Synthese, korrekten FSM-Beschreibungen, der Vermeidung von Problemen auf weiteren Designstufen, Takten und Reset-Tree-Problemen, CDC, RDC, DFT und Codierung für Portabilität und Wiederverwendung. Die Software führt eine statische Analyse auf Basis von RTL- und SDC™-Quelldateien durch und deckt kritische Design-Probleme frühzeitig im Design-Zyklus auf, was wiederum die Design-Abnahmezeiten drastisch reduziert. Die Ausführung von ALINT-PRO vor der RTL-Simulation und der Logiksynthese verhindert, dass sich Design-Probleme in die nachgelagerten Phasen des Design-Flows ausbreiten und reduziert die Anzahl der Iterationen, die zur Fertigstellung des Designs erforderlich sind.

Single Framework für DRC and CDC/RDC Analyse

ALINT-PRO verfügt über ein gut durchdachtes, intuitiv zu bedienendes Framework, das Funktionen für eine effiziente Design-Analyse bietet, darunter RTL-Schaltplan-Viewer, FSM-Viewer, Takt- und Reset-Viewer, Schaltplan-Viewer, Elaboration-Viewer, Violation-Viewer und spezielle Werkzeuge wie CDC-Viewer, RDC-Viewer und CDC-Schaltplan für die Analyse von Takt- und Reset-Domain-Crossings.

Das Einrichten eines bestehenden HDL-Designs für die Analyse in ALINT-PRO wird unterstützt durch das Einlesen externer Projektdateiformate (Aldec Active-HDL, Aldec Riviera-PRO, Xilinx Vivado, Xilinx ISE, Intel Quartus), das Interpretieren typischer Simulationsskripte (Kompatibilitätsbefehle wie vcom, vlog, vsim, vlib) sowie traditioneller Dateilisten für die Batch-Modus-Tools und sehr einfache GUI-Assistenten für den direkten Import einzelner Dateien und ganzer Verzeichnisse.

Full Chip-Level Linting vs. Unit Linting

Beim Full-Chip-Level-Linting wird die Design-Hierarchie als Ganzes analysiert, wobei bestimmte Werte generischer Parameter von den Top-Level-Instanzen bis hinunter zu den Leaf-Submodulen propagiert werden und die benutzerdefinierten Timing-Constraints angewendet werden. Diese Methodik ist traditionell für typische HDL-Linting-Tools und wird häufiger während der Signoff-Phase oder für Verifikationstypen verwendet, die eine Untersuchung des gesamten Designs auf einmal als bereits integriertes System erfordern (Takt- und Reset-Checks, CDC, RDC, DFT). Diese Methodik geht davon aus, dass das gesamte oder zumindest der größte Teil des zu testenden Designs bereits implementiert ist.

Unit Linting ist ein relativ neuer Ansatz, der sich gut mit einem flachen Elaborationsmodus kombinieren lässt – eine spezielle Art der Elaboration, die HDL-Entwurfseinheiten unabhängig voneinander isoliert betrachtet und die Standardwerte von generischen Parametern verwendet. Dieser Verarbeitungsstil verzeiht in hohem Maße fehlende Elemente in Designs, wie z. B. noch nicht implementierte Teile der Hierarchie. Dies macht das Unit Linting sehr wertvoll, sowohl wenn es auf einzelne Quelldateien angewendet wird, unabhängig von anderen Dateien, als auch direkt nachdem Dateien von einem Designer geändert wurden. Viele sehr wertvolle Regelprüfungen werden daher sehr früh, sogar fast unmittelbar nach dem Schreiben des Codes selbst, aktiviert, wodurch die Feedback-Schleife für den Designer von Tagen oder Wochen auf nur wenige Sekunden verkürzt wird. Eine natürliche Anwendung für Unit Linting ist die Integration mit HDL-Editoren, wobei das Unit Linting im Hintergrund abläuft, was in den neuesten Versionen von Aldec Active-HDL™ und Riviera-PRO™ sowie in einigen der beliebten HDL-Editoren von Drittanbietern vorgesehen ist.

Unit-Linting macht die Anwendung von vollständigem traditionellem Linting nicht überflüssig, da die Kombination von unabhängigen Units nach der Integration zusätzliche Probleme verursachen kann. Die systematische Anwendung von Unit Linting kann jedoch den Verifizierungsaufwand während der Abnahmen drastisch reduzieren.

Prüfen von FPGA-Designs

ALINT-PRO unterstützt problemlos die Ausführung von Regelprüfungen für Designs, die auf eine FPGA-Implementierung mit Xilinx-, Altera-, Microsemi- und Lattice-Technologien abzielen, und das bei minimaler Einrichtung. ALINT-PRO bietet die neuesten Versionen der FPGA-Herstellerbibliotheken, die vorgefertigt, standardmäßig installiert und für erweiterte Timing- und CDC-Regelprüfungen vorkonfiguriert sind.

ALINT-PRO automatisiert die Einrichtung des hierarchischen und inkrementellen Analyseflusses für IP-basierte FPGA-Designs. Jeder IP-Block kann zunächst separat analysiert werden, und die extrahierten Timing-Constraints können für eine viel schnellere Design-Analyse auf höherer Ebene weitergeleitet und wiederverwendet werden. Sofern der IP-Block nicht in der ursprünglichen Designumgebung neu konfiguriert wird, wird sein Aufbau nur einmal analysiert, was bei den nachfolgenden Durchläufen des Haupt-FPGA-Designs viel Zeit spart.

Abläufe im Batch-Modus

Die wichtigsten Funktionen von ALINT-PRO sind auch über einen umfangreichen Satz von TCL-basierten Skriptbefehlen zugänglich. Die Skripte können zur Automatisierung von Entwurfsregelprüfungen, sich wiederholenden Einstellungen und der Erstellung von Berichten verwendet werden. Die Skripte können in einer interaktiven Konsolen-Shell oder im vollautomatischen Batch-Modus ausgeführt werden. Schließlich ist ALINT-PRO in der Lage, die typischsten Design-Eingabe- und Linting-Szenarien im echten Batch-Modus mit einem einzigen Kommandozeilen-Shell-Anwendungsaufruf auszuführen, was es perfekt für die Integration in größere Regressionstest-Skripting- und Continuous-Integration-Umgebungen wie Jenkins geeignet macht.

Verfügbare Regelbibliotheken für ALINT-PRO™

ALINT-PRO enthält Regelbibliotheken, die auf STARC- (Semiconductor Technology Academic Research Center) und RMM- (Reuse Methodology Manual) Designrichtlinien basieren, welche die von Halbleiterunternehmen auf der ganzen Welt verwendeten Best Practices in der Designentwicklung nutzen. Für sicherheitskritische Designs liefert Aldec Regelbibliotheken, die auf DO-254-Richtlinien basieren und sich auf die Analyse kritischer Probleme konzentrieren, die die Stabilität des Designs beeinflussen. Für die RISC-V Design Community bietet ALDEC das RISC-V Regel-Plugin an, das auf den in der Industrie bewährten Best-IP-Design-Praktiken und Richtlinien basiert.

Die wichtigsten Regel-Plugins werden durch hochkonfigurierbare Aldec Basic- und Premium-Regelbibliotheken ergänzt, die auf Aldec-eigener Erfahrung mit FPGA- und ASIC-Digitaldesign basieren sowie viele Ergänzungen enthalten, die von bestehenden ALINT-PRO-Kunden empfohlen wurden und gegen Chip-Killer-Probleme in Designs im industriellen Maßstab kämpfen. Das ALDEC SV Plugin zielt auf neue Varianten von RTL-Fehlern ab, die spezifisch für SystemVerilog-Design-Subsets sind.

Das ALDEC_CDC Regel-Plugin verwandelt ALINT-PRO in eine vollwertige CDC- und RDC-Verifikationslösung, die in der Lage ist, komplexe Clock- und Reset-Domain-Crossings zu analysieren und Metastabilitätsprobleme in modernen Multi-Clock- und Multi-Reset-Designs zu behandeln. Die Verifikationsstrategie in ALINT-PRO besteht aus drei Schlüsselelementen: statische strukturelle Verifikation, Design Constraints Setup und dynamische funktionale Verifikation. Die ersten beiden Schritte werden in ALINT-PRO ausgeführt, während die dynamischen Prüfungen über die Integration mit Simulatoren (Riviera-PRO™ , Active-HDL™ und ModelSim® werden unterstützt) auf der Grundlage der automatisch generierten Testbench durchgeführt werden. Durch diesen Ansatz werden potenzielle Metastabilitätsprobleme während der RTL-Simulation aufgedeckt, für deren Erkennung ansonsten Labortests erforderlich wären. Die Fehlersuche bei CDC- und RDC-Problemen erfolgt über umfangreiche Schaltplan- und HDE-Cross-Probing-Mechanismen sowie über umfassende Berichte und eine TCL-basierte API, die das Durchsuchen von Syntheseergebnissen, Takt- und Reset-Strukturen, erkannten Takt- und Reset-Domain-Crossings und identifizierten Synchronisierern ermöglicht.

Features

Analyse von Takt- und Reset-Netzwerken

Vermeidung von Post-RTL- und Post-Synthese-Simulations-Fehlanpassungen

Verifizierung der Korrektheit von FSM-Beschreibungen

Grafische Untersuchung der extrahierten FSMs und der identifizierten FSM-Probleme

Code-Portabilität und Wiederverwendung

Umfassende CDC- und RDC-Prüfungen mit dem ALDEC_CDC-Regel-Plug-in

Erweiterte CDC- und RDC-Debugging-Umgebung

Schaltplan-Viewer

DFT-Prüfungen

SDC™-Support