FPGA-Designerstellung und FPGA-Simulation

Active-HDL™ ist eine Windows®-basierte, integrierte FPGA-Design-Erstellungs- und Simulationslösung für teambasierte Entwicklungsumgebungen. Die integrierte Design-Umgebung (IDE) von Active-HDL umfasst eine vollständige HDL- und grafische Design-Tool-Suite sowie einen RTL/Gate-Level-Mixed-Language-Simulator für die schnelle Entwicklung und Verifizierung von FPGA-Designs.

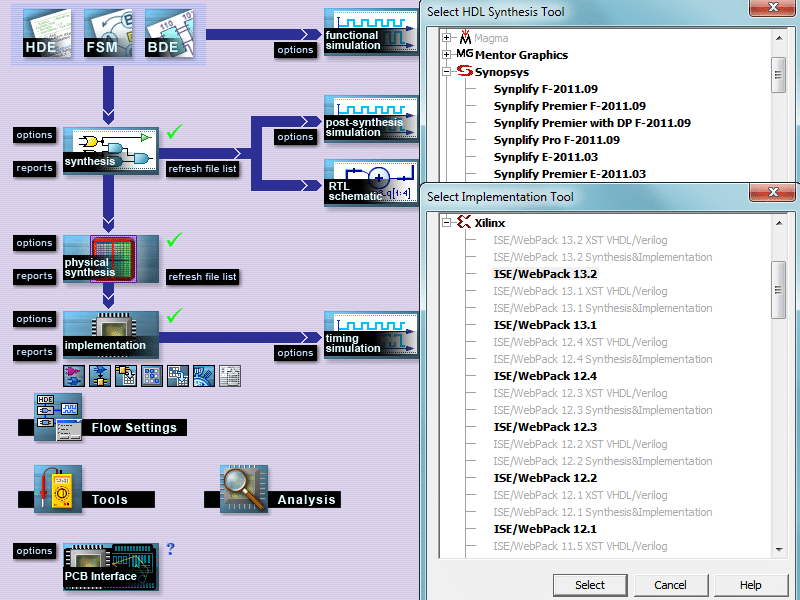

Der Design-Flow-Manager ruft über 200 EDA- und FPGA-Tools während der Design-Eingabe, der Simulation, der Synthese und des Implementierungsflusses auf und ermöglicht es den Teams, während des gesamten FPGA-Entwicklungsprozesses auf einer gemeinsamen Plattform zu bleiben. Active-HDL unterstützt branchenführende FPGA-Bausteine von Intel®, Lattice®, Microsemi™ (Actel), Quicklogic®, Xilinx® und anderen.

Top-Funktionen und Vorteile

Projektmanagement

- Einheitliches teambasiertes Design Management sorgt für Einheitlichkeit in lokalen oder entfernten Teams

- Konfigurierbare FPGA/EDA-Flow-Manager-Schnittstellen zu den Tools von über 200 Anbietern ermöglichen es den Teams, während der gesamten FPGA-Entwicklung auf einer Plattform zu bleiben

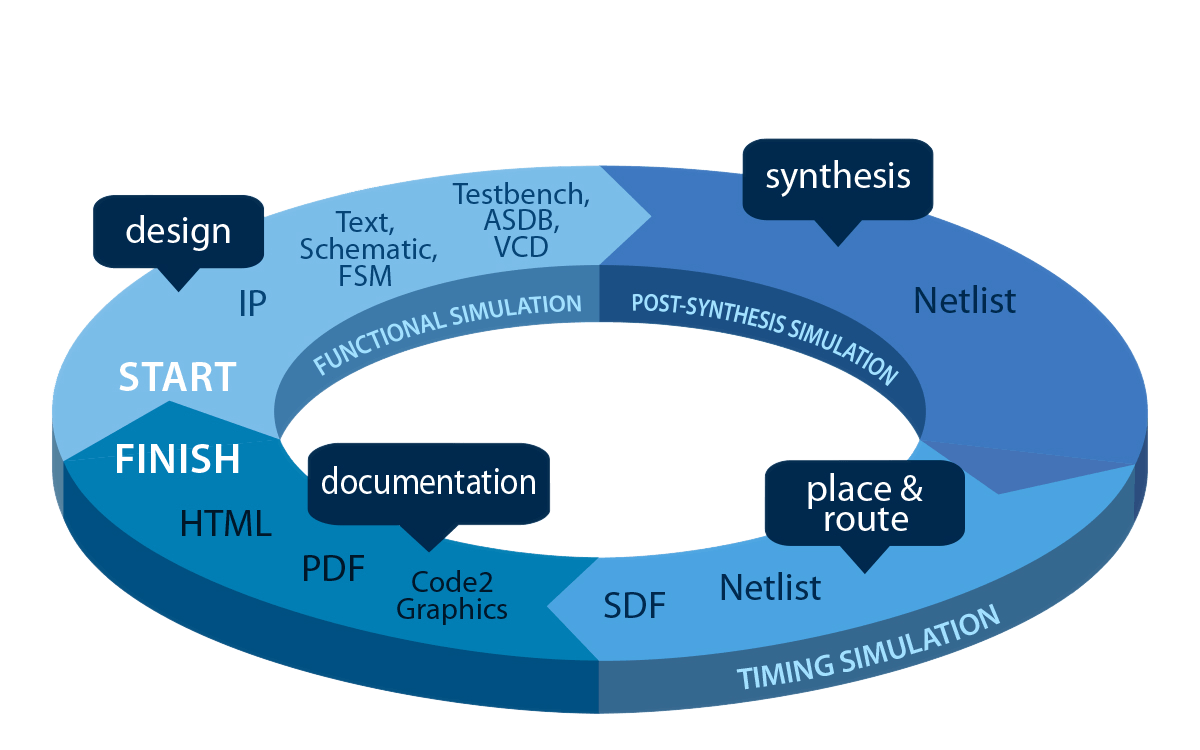

Ein typischer FPGA-Designflow umfasst die Designeingangsphase, die Synthese und die Implementierung (Fitting und Place & Route-Verarbeitung), wobei auf jede Phase typischerweise eine Simulation folgt. Die Verwaltung des Projekts während des gesamten Design-Flows zusammen mit den Design-Daten wird sehr wichtig. Der Design Flow Manager ist das Werkzeug, das diese Prozesse automatisieren soll. Er bietet Schnittstellen zu den Tools von Drittanbietern und stellt FPGA-Designern eine einzigartige Plattform zur Verfügung, die während des gesamten FPGA-Design-Flows verwendet werden kann.

Vorteile der Verwendung des FPGA-Projektmanagements:

- Umfasst den gesamten FPGA-Design-Flow von der Design-Eingabe bis hin zu Place und Route, was bedeutet, dass Sie sich in den verschiedenen Phasen des FPGA-Designs nicht in verschiedene Hersteller-Tools einarbeiten müssen

- Bietet Schnittstellen zu mehr als 90 Hersteller-Tools, die es Ihnen ermöglichen, Ihren Flow auf viele verschiedene Arten zu konfigurieren

- Arbeitet mit dem Versions-/Revisionskontrollsystem zusammen, um Daten- und Versionsmanagement für Ihr Projekt bereitzustellen

- Die eingebaute Server-Farm ermöglicht es Designern, die Warteschlange für ihre Simulations-, Synthese- und Implementierungsaufgaben zu verwalten

Grafische/Text-Design-Eingabe

- Schnelles Deployment von Designs durch Verwendung von Text, Schema und State Machine

- Verteilen oder liefern Sie IPs mit dem sicheren und zuverlässigen Interoperable Encryption Standard

Schaltplan-/Blockdiagramm-Editor

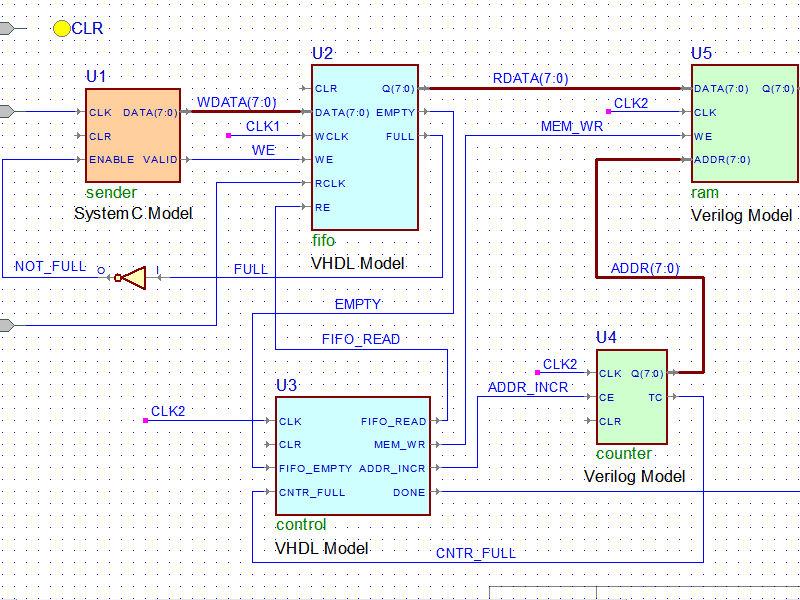

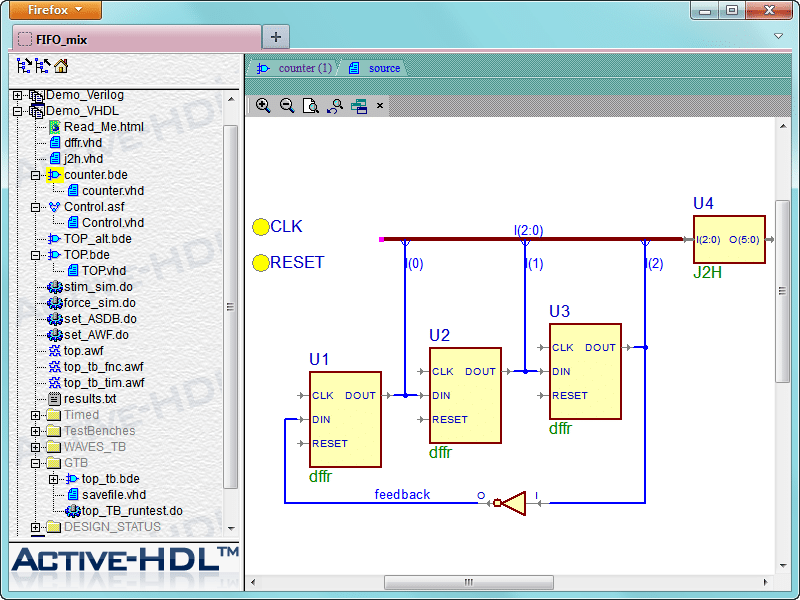

Der Blockdiagramm-Editor ist ein Werkzeug zur grafischen Eingabe von VHDL-, Verilog- und EDIF-Designs. Wenn Ihr HDL-Design zu einem großen Teil strukturell ist, kann es für Sie einfacher sein, seine Beschreibung grafisch als Blockdiagramm einzugeben, als den Quellcode zu schreiben. Der Blockdiagramm-Editor wandelt das Diagramm dann automatisch in eine strukturelle VHDL-, Verilog- oder EDIF-Netzliste um. Mit Active-HDL können Sie beide Arten der Beschreibung mischen. Zum Beispiel kann die Top-Level-Design-Entity ein Blockdiagramm sein, während die darin instanziierten Komponenten mit HDL-Code/EDIF-Netzliste und/oder Zustandsdiagrammen beschrieben werden.

- Der Schaltplan-Editor unterstützt sowohl Bottom-up- als auch Top-down-Methoden

- Schaltplanbibliotheken für Hersteller ermöglichen Ihnen die Erstellung technologieorientierter Blockdiagramme

- Die hierarchische Eigenschaft des Editors hilft Ihnen, mehrere Seiten des Schaltplans für komplexe Blöcke zu erstellen

- Blockdiagrammdateien können in VHDL, Verilog oder EDIF-Netzliste übersetzt werden

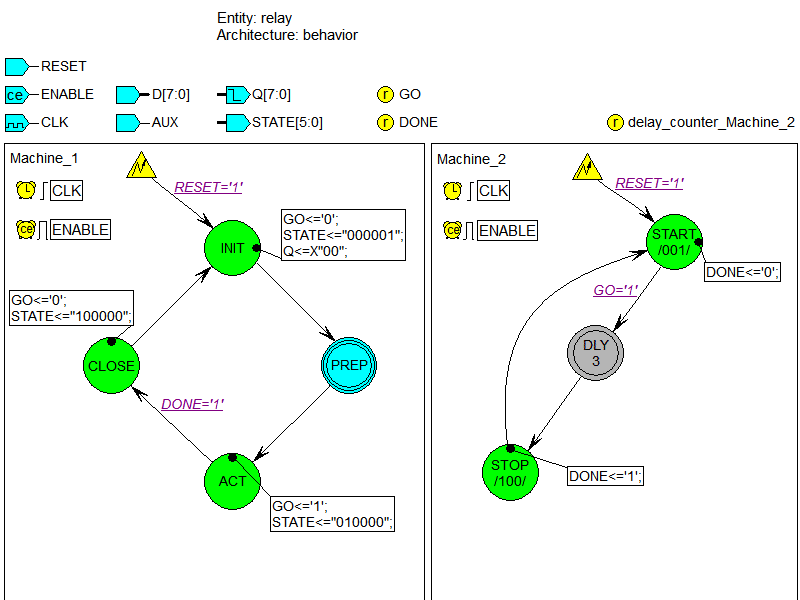

State Machine Editor

Der Zustandsdiagramm-Editor ist ein Werkzeug zur grafischen Bearbeitung von Zustandsdiagrammen von synchronen und asynchronen Maschinen. Das Zeichnen eines Zustandsdiagramms ist ein alternativer Ansatz für die Modellierung eines sequentiellen Geräts. Anstatt den HDL-Code selbst zu schreiben, können Sie die Beschreibung eines Logikblocks als grafisches Zustandsdiagramm eingeben. Der Editor generiert dann automatisch den HDL-Code auf der Grundlage der eingegebenen grafischen Beschreibung. Aufgrund der intuitiven grafischen Form sind Zustandsdiagramme leicht zu erlernen und weitaus besser lesbar als der HDL-Code.

Vorteile der Verwendung des State Machine Editors:

- Er bietet eine visuelle Karte, die den Fluss, die Ereignisse und Aktionen von Zustand zu Zustand spezifiziert, was viel einfacher zu lesen und zu verstehen ist

- Der eingebaute Testbench-Generator kann helfen, Ihren Zustandsautomaten sehr schnell zu verifizieren

- Es kann als großartiges Kollaborationswerkzeug während Design-Meetings dienen, da sie einfach zu verstehen und zu erklären sind

- Sie können verwendet werden, um das Design auf verschiedenen Abstraktionsebenen zu dokumentieren

HDL Text Editor

Der HDL-Editor ist ein Texteditor, der für die Bearbeitung eines HDL-Quellcodes konzipiert ist. Er ist eng mit dem Compiler und Simulator integriert, um Debugging-Funktionen zu ermöglichen. Einige der wichtigsten Funktionen des HDL-Texteditors sind die Hervorhebung von Schlüsselwörtern (VHDL, Verilog/SystemVerilog, C/C++, SystemC, OVA und PSL), die Unterstützung von Code-Gruppen und Code-Strukturen, die automatische Vervollständigung und automatische Formatierung, Lesezeichen und benannte Lesezeichen für eine einfache Navigation durch den Quellcode, Haltepunkte und Spaltenauswahl

Vorteile der Verwendung des HDL-Texteditors:

- Cross-Probing zwischen Waveform-Viewer und HDL-Texteditor erleichtert die Fehlersuche

- Signale können direkt vom HDL-Editor zum Waveform-Viewer hinzugefügt werden

- Unterstützt Live-Value-Probes im Quellcode während der Simulation

- Sprachvorlagen für VHDL, Verilog, SystemVerilog und SystemC helfen beim schnellen Schreiben von Code

Simulation und Debugging

- Leistungsstarker Common-Kernel-Mixed-Language-Simulator, der VHDL, Verilog, SystemVerilog und SystemC unterstützt

- Sicherstellung der Code-Qualität und -Zuverlässigkeit durch grafisch interaktives Debugging und Code-Qualitätswerkzeuge

- Metrikgesteuerte Verifikation, um nicht ausgeführte Teile Ihres Designs mithilfe von Code-Coverage-Analysetools zu identifizieren

- Verbessern Sie die Verifikationsqualität und finden Sie mehr Bugs mit ABV – Assertion-Based Verification (SVA, PSL, OVA)

- Möglichkeit zur Simulation von fortgeschrittenen Verifikationskonstrukten wie SV Functional Coverage, Constrained Randomization und UVM

- Schließt die Lücke zwischen HDL-Simulation und mathematischer High-Level-Modellierungsumgebung für DSP-Blöcke mit der MATLAB®/Simulink®-Schnittstelle

SystemVerilog-Simulation

SystemVerilog ist eine leistungsfähige, vom IEEE genehmigte Sprache (IEEE 1800™), die erhebliche Verbesserungen gegenüber ihrem Vorgänger, Verilog HDL, ermöglicht. Diese umfangreiche Sprache kombiniert viele der besten Eigenschaften von VHDL, Verilog und C++ und bietet ausgezeichnete Möglichkeiten für Systemarchitektur, Design und Verifikation.

SystemVerilog gliedert sich in drei Hauptbereiche: Hardwarebeschreibung, Assertions und die Testbench-Sprache. Je nach Konfiguration des Werkzeugs und der Lizenz können Designer Funktionen aus diesen verschiedenen Bereichen der Sprache nutzen. Die auf SystemVerilog basierende Universal Verification Methodology (UVM) ist eine industrieerprobte und von Accellera genehmigte funktionale Verifikationsmethodik. Aldec bietet eine vorkompilierte UVM-Bibliothek und einen SystemVerilog-Simulator an, um Kunden bei der Verifikation der komplexen Designs von heute zu unterstützen.

VHDL Simulation

Der VHDL IEEE 1076-2008 Sprachstandard ist ein leistungsfähiges, benutzerfreundlicheres Upgrade von früheren Versionen. VHDL-2008 fügt wichtige Spracherweiterungen für Verifikations- und Design-Ingenieure hinzu und bietet viele Vorteile durch zahlreiche hinzugefügte Funktionalitäten, darunter: PSL-Einbindung (Unterstützung von Properties und Assertions), IP-Schutz (Kompilierung verschlüsselter Dateien), VHPI, Festkomma- und Fließkomma-Packages, Generics-Packages, neue Typen (integer_vector und boolean_vector, etc.), Verfahren für kombinatorische Logik, vereinfachte Conditional- und Case-Anweisungen, erweiterte Zuweisungen, neue und verbesserte Operatoren, erweiterte Bitstring-Literale, verbesserte Port-Maps, Kontextdeklarationen und Klauseln.

Aldec unterstützt VHDL-2008 sowohl in Active-HDL™ als auch in Riviera-PRO™ ohne zusätzliche Kosten für Kunden mit einem gültigen Wartungsvertrag und mit einer VHDL- oder gemischtsprachigen Simulationskonfiguration.

SystemC Co-Simulation

SystemC ist eine Umgebung, die die Beschreibung und Verifizierung von digitalen Systemen mit C++ ermöglicht. Es unterliegt der IEEE 1666™-2005 und wurde ursprünglich von der OSCI (Open SystemC Initiative) entwickelt. Es handelt sich um eine Bibliothek von Klassen und Vorlagen, die hardware- und systembezogene Funktionen bieten, die in Standard-C++ nicht verfügbar sind.

Sowohl die Simulations- und Verifikationssoftwarelösungen Active-HDL als auch Riviera-PRO unterstützen C/C++ und SystemC und bieten Entwicklern die Möglichkeit zur nahtlosen Integration von HDL-Code und den verschiedenen C-Varianten. Diese IEEE-standardisierten Schnittstellen ermöglichen die Simulation von HDL-Modellen mit High-Level-C-basierten Testbenches, die Instanziierung von C-Modellen in HDL, die Verbindung von benutzerdefinierten Visualisierungsanwendungen mit HDL, die Durchführung von TLM und mehr.

Die C/C++/SystemC-Umgebung ist nach der Installation sofort einsatzbereit. Das Installationsprogramm enthält einen unterstützten C/C++-Compiler, Header-Dateien und Bibliotheksdateien, die von verschiedenen Typen von C-Anwendungen (SystemC, SystemC+SCV, PLI, VHPI) benötigt werden. C-Anwendungen können mit einem speziellen Befehl kompiliert werden, der die erforderlichen Defines, Pfade zu Header-Dateien, zu linkenden Bibliotheken usw. festlegt. Dadurch können sich die Ingenieure auf die Entwicklung konzentrieren und müssen sich nicht mit den Tücken von C++-Compilern herumschlagen. Ein leistungsfähiges Set von Debugging-Tools ist mit den Aldec-Lösungen ebenfalls verfügbar.

Die Simulatoren von Aldec enthalten auch eine komplette Umgebung für die Entwicklung und Simulation von SystemC Verification Library (SCV) Anwendungen. Die kürzlich populär gewordene SCV baut auf der Grundlage von SystemC und Testbuilder auf und unterstützt fortschrittliche Randomisierungstechniken, Transaktionsaufzeichnung usw. Header-Dateien und vorkompilierte Bibliotheksdateien werden mit den Aldec-Produkten mitgeliefert.

Dokumentation HTML/PDF

- Stellen Sie sie das Design in leicht verständlicher grafischer Form mit dem HDL-zu-Schaltplan-Konverter dar

- Schnelle Weitergabe von Designs mit automatisch generierter Design-Dokumentation in HTML und PDF

Ein integriertes Dokumentationswerkzeug innerhalb von Active-HDL ermöglicht Ihnen die Erstellung einer Textdarstellung und einer grafischen Darstellung Ihres Arbeitsbereichs oder Designs in HTML oder PDF. Alle Entwurfselemente wie Entwurfsdateien, Wellenformen, Blockdiagramme und angehängte Dokumente können in HTML- oder PDF-Dokumente exportiert werden.

Vorteile der Verwendung von Dokumentation:

- Sie ist äußerst hilfreich für die Prozesse wie Design-Reviews, Wiederverwendung und Archivierung

- Die resultierenden Dokumente behalten immer die Hierarchie des Designs bei, was eine einfache Navigation in komplexen Designs ermöglicht

- Durch die Möglichkeit, Vektorgrafiken darzustellen, bleibt die hohe Auflösung von Schaltplandateien im generierten Dokument erhalten, wodurch es leicht zu lesen oder zu drucken ist

- Das HTML-Format wird in jedem Webbrowser unterstützt. Auf diese Weise können Entwürfe/Arbeitsbereiche und deren Dokumentation an Benutzer weitergegeben werden, die sie analysieren möchten, ohne auf Active-HDL zuzugreifen.

- HTML-Projekte können in einem lokalen Intranet-Netzwerk oder im Internet veröffentlicht werden