IDesignSpec™ GDI

Automatisierung der Halbleitertechnik der nächsten Generation

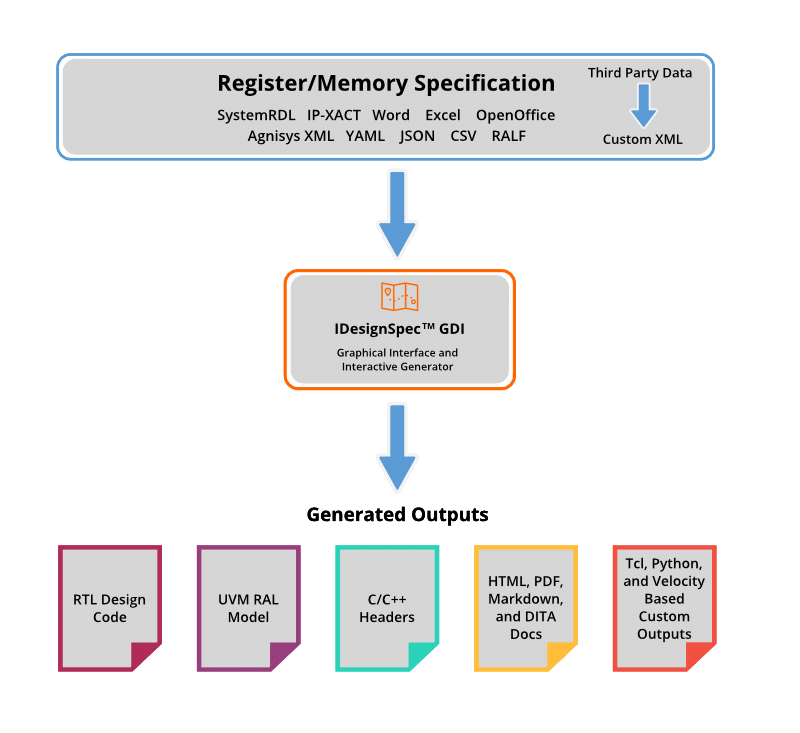

Agnisys IDesignSpec GDI (Graphical Design Interface) bietet eine Komplettlösung für die ausführbare hierarchische Spezifizierung Ihrer Speicher, Registersätze, Register und Registerfelder in einer IP oder einem SoC. Sie können aus einer Vielzahl von Eingabeformaten wählen. Sie können vorhandene Beschreibungen in Standardformaten wie SystemRDL-, IP-XACT-, JSON-, RALF-, YAML-, XML- und CSV-Dateien (Comma-Separated Values) importieren.

Leistungsstarker Register- und Memory-Editor, SystemVerilog, UVM

Für ein Maximum an Nutzen und Flexibilität können Sie den hochgradig intuitiven spezialisierten Register- und Speichereditor wählen, der in IDesignSpec GDI enthalten ist, einer grafischen Benutzeroberfläche (GUI) für die Eingabe von Spezifikationen. IDesignSpec GDI generiert interaktiv eine Vielzahl von Ausgabedateien für die an Ihrem Projekt beteiligten Teams und unterstützt damit Design, Verifikation, Embedded Programming, Validierung und Dokumentation.

IDesignSpec GDI fügt sich nahtlos in Ihren SoC- oder IP-Entwicklungsablauf ein, einschließlich der Integration mit dem Git-Revisionskontrollsystem, um sowohl Text- als auch Grafikdateien zu verwalten und die Zusammenarbeit zu fördern.

Wie IDesignSpec GDI Ihren Entwicklungsprozess verbessert

Diese ausführbaren Spezifikationen, die von IDesignSpec GDI gelesen werden, unterstützen sowohl einfache Register als auch mehr als 400 spezielle Registertypen, darunter indirekte, indizierte, Nur-Lese/Schreib-Register, Alias-Register, Lock-Register, Shadow-Register, FIFO-Register, Puffer-Register, Interrupt-Register, Zähler-Register, Paged-Register, virtuelle Register, externe Register, Lese/Schreib-Paare und Kombinationen dieser Typen.

RTL-Generierung von Registern, Speichern, CDC-Logik und erweiterter Buskonnektivität

IDesignSpec GDI generiert aus Ihren Spezifikationen interaktiv Ausgabedateien für Ihre Design-, Verifikations-, Software- und Dokumentationsteams. Sie generiert die vollständige RTL-Beschreibung für die Register und Speicher, einschließlich eines Bus-Slave und einer Dekodierlogik, die für das vom Benutzer ausgewählte Busprotokoll spezifisch ist, sowie einer CDC-Synchronisationslogik (Clock-Domain-Crossing). Dies ermöglicht den sofortigen Anschluss Ihres Designs an den Registerbus. Zu den unterstützten Schnittstellen gehören APB, AHB, AHB-Lite, AXI4, AXI4-Lite, TileLink, Avalon, Wishbone und proprietäre Busse.

Der generierte SystemVerilog-, Verilog-, VHDL- oder SystemC-RTL-Code für die Register ist leicht lesbar und mit leicht verständlichen Kommentaren versehen. Ihr Hardware-Entwicklungsteam fügt die generierten Dateien einfach zu seiner Liste der handgeschriebenen RTL-Blöcke für Anwendungslogik und IP-Blöcke von Drittanbietern hinzu, um sie mit Simulation, Logiksynthese und anderen Tools im Entwicklungsfluss zu verwenden.

Generierung von SystemVerilog-Testbench-Modellen und C/C++-Headern

IDesignSpec GDI generiert ein SystemVerilog-Modell, das mit dem UVM-Standard kompatibel ist und in Ihre UVM-Testbench integriert werden kann. Dies erspart Ihrem Design- und Verifikationsteam eine Menge Arbeit. IDesignSpec GDI hilft auch Ihren Embedded-Programmierern, indem es C/C++-Header für die Speicher, Register und Felder generiert. Dies ersetzt die mühsame manuelle Transkription von Spezifikationsdetails in Code und vermeidet die Gefahr von Fehlern während des Prozesses.

Generierung von hochwertiger Dokumentation aus der Spezifikation

Für Ihre technischen Redakteure generiert IDesignSpec GDI eine hochwertige Dokumentation von Registern und Speichern, die sich für die Aufnahme in Benutzerhandbücher eignet. Zu den vom Benutzer auswählbaren Formaten gehören Microsoft Word, HTML, PDF, Markdown und DITA.