Fortschritte bei FPGA-Silizium, Tool-Flows und IPs haben bewiesen, dass FPGAs die ideale Lösung für die Beschleunigung komplexer Berechnungsanwendungen zur Lösung wissenschaftlicher, technischer und wirtschaftlicher Probleme sind. Die inhärente Reprogrammierbarkeit von FPGAs, tiefe Pipelining-Strukturen und massive parallele Rechenressourcen begünstigen die sich ständig weiterentwickelnde Technologie von High Performance Computing (HPC)-Algorithmen und -Anwendungen in Bereichen wie Genomik, Kryptographie, Computer Vision, neuronale Netze, Big Data und Hochfrequenzhandel. Darüber hinaus kann FPGA bei gleichen oder sogar besseren Ergebnissen den Stromverbrauch drastisch reduzieren und bietet Platz für zukünftige Upgrades und Modifikationen.

Seit mehr als 30 Jahren stellt Aldec Werkzeuge für FPGA-Design und -Verifikation bereit und hat sich so ein umfangreiches Wissen über FPGA-Technologie, Industriestandards, Werkzeugketten, Hardware-Programmiersprachen und Verifikationsmethoden angeeignet. Aldec’s Ziel ist es, diese Erfahrung zu teilen, damit die energieeffizienteste HPC-Lösung eingesetzt werden können die heute verfügbar sind. Im Gegensatz zu anderen Anbietern, die reine Hardware liefern, unterstützen Aldec den Migrationsprozess beim FPGA mit Entwicklungswerkzeugen, wiederverwendbaren Modulen und Beratungsleistungen. Die schlüsselfertigen HPC-Lösungen von Aldec umfassen drei Elemente, die für die Beschleunigung und den Einsatz von HPC-Algorithmen mit skalierbarer FPGA-basierter Hardware erforderlich sind.

- FPGA-basierte Beschleuniger

- Referenzdesigns und Integrationsdienstleistungen

- HDL/RTL-Codeentwurf und Simulationswerkzeuge

FPGA-Beschleuniger

Die Bedürfnisse jedes Kunden sind unterschiedlich und hängen von den jeweiligen Projekten ab. Daher hat Aldec ein Portfolio von FPGA-Beschleunigerkarten entwickelt, um die verschiedenen Bedürfnisse zu decken. Derzeit bietet Aldec mehrere Board-Konfigurationen an, die für die Beschleunigung der anspruchsvollsten und ausgefeiltesten Algorithmen geeignet sind und in zwei Hauptkategorien fallen – Large Scale HPC und Embedded HPC.

Die FPGA-Beschleuniger, die aus der Familie der HES-Prototyping-Boards hervorgegangen sind, wurden für HPC-Anwendungen im großen Maßstab entwickelt und optimiert. Um den wachsenden Anforderungen des Embedded HPC gerecht zu werden, hat Aldec eine spezielle Familie von kompakten TySOM-Boards entwickelt, die Xilinx Zynq-Bausteine verwenden, die sowohl ARM Cortex-Prozessoren als auch FPGAs in einem Chip integrieren.

Schnelle Integration

Kurze Entwicklungszeiten von Algorithmen, die auf FPGAs abgebildet werden, und eine schnelle Integration in die Hauptanwendung sind das, was Softwareentwickler brauchen und fordern. Aldec versteht die HPC-Geschäfts- und Softwareentwicklungsmodelle sowie FPGA-Design-Prozesse. Daher sind Sie in der Lage, Integrationslösungen anzubieten, die es Ihnen ermöglichen, die Vorteile der FPGA-Technologie zu nutzen und die Einstellung eines Teams von Hardware-Experten zu vermeiden. Die Integrationslösungen umfassen wiederverwendbare Software- und Hardwarekomponenten, wie z.B. die HES Proto-AXI-Schnittstelle, sowie Beratungsleistungen zur Vermittlung des Wissens und Aldec’s Erfahrung. Die enge Zusammenarbeit von Aldec mit FPGA-Chip-Anbietern und die umfassende Kenntnis der für die Algorithmus-Implementierung verwendeten Toolchains machen Ihren Übergang zu FPGA effizient und problemlos.

Dienstleistungen & Referenzdesigns

Aldec glaubt an die Wiederverwendbarkeit und bietet deswegen den Kunden zahlreiche Referenzdesigns, sowohl für Large Scale HPC- als auch für Embedded HPC-Plattformen. Die Kunden von Aldec müssen ihre Projekte nicht von Grund auf neu beginnen, sondern können vorhandene Designs wiederverwenden, was die Projektlaufzeit erheblich verkürzt. Sollte dies nicht ausreichen, kann Aldec mit seiner über 30-jährigen Erfahrung in der FPGA/ASIC-Technologie kundenspezifische Entwicklungsdienstleistungen anbieten und durchführen wie z.B.:

- Aufbau eines kompletten Systems, das für Ihre Anwendung optimiert ist

- Integration Ihrer Algorithmen in die FPGA-Hardware-Infrastruktur

- Konvertierung eines Algorithmus auf den FPGA

FPGA-Design- und Simulationswerkzeuge

Anwender, die ein komplettes FPGA-Entwicklungs-Ökosystem suchen, profitieren von der Zusammenarbeit mit Aldec mit seinen FPGA-Beschleunigerkarten und RTL-Entwicklungs-/Simulationswerkzeugen wie Riviera-PRO – einem leistungsstarken Mixed-Language-Simulator (VHDL/Verilog/SystemVerilog/SystemC) mit Python-Testbench-Unterstützung für FPGAs.

Vorteile

- Maßgeschneiderte Hardware-Plattformen – Benutzer können aus einem großen Portfolio von FPGA-Boards für groß angelegte und eingebettete HPC-Anwendungen wählen.

- Skalierbarkeit – die Replikation von Algorithmus-Kernels wird durch die Unterstützung von Multi-FPGA- und Multi-Board-Konfigurationen erleichtert

- Schnelle Integration und kurze Inbetriebnahme durch wiederverwendbare Komponenten, Prozesse und Referenzdesigns

- Vollständige Entwicklungsumgebung einschließlich RTL-Simulatoren und Integration mit Tools von FPGA-Anbietern

Computer Vision

Computer Vision, bei denen Bildverarbeitungs-Algorithmen erforderlich sind, ist eine der sich am dynamischsten entwickelnden Anwendungen, die von der FPGA-Rechenleistung profitieren. Die Erkennung von sich bewegenden Objekten ist sowohl in Überwachungssystemen als auch in verschiedenen industriellen Fällen während der automatisierten Produktion von Bedeutung.

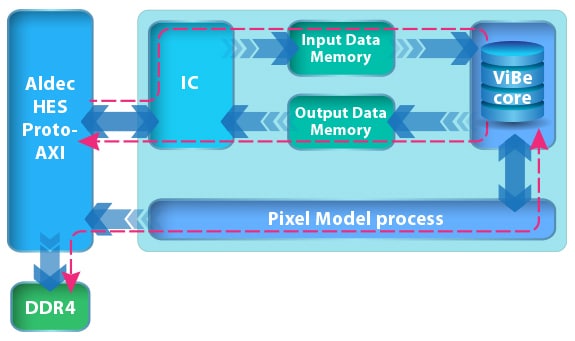

Aldec hat ein Demo-Design entwickelt, das zeigt, wie FPGAs zur Beschleunigung von Bildverarbeitungsalgorithmen eingesetzt werden können, die eine große Menge an Eingangsdaten verarbeiten und mit hohen Eingangs- und Ausgangsbandbreiten zurechtkommen. Das Demo-Design bietet eine RTL-Implementierung eines Bewegungserkennungsalgorithmus namens ViBe und einen Anwendungsfall zur Erkennung von sich bewegenden Objekten in einem Videodatenstrom. Das Beispiel zeigt auch, dass die Ausführung des Algorithmus weiter beschleunigt werden kann, indem der ViBe-Funktionskern repliziert wird und die Videoverarbeitung in parallelen Threads unter effizienter Nutzung der Ressourcen eines großen FPGAs, Xilinx Virtex UltraScale XCUS440, erfolgt. Es wird auch demonstriert, wie ein im FPGA laufender Algorithmus-Kernel über die Aldec HES Proto-AXI-Schnittstelle mit der PC-Host-Workstation verbunden werden kann oder wie man auf das On-Board-DDR zugreifen kann.

Wichtigste Funktionen

- Funktion: Erkennung bewegter Objekte im Videodatenstrom

- Algorithmus: Vibrierende Bewegungserkennung

- Verarbeitung des Live-Datenstroms von der an den Host angeschlossenen USB-Kamera

- Video-Auflösung: Full-HD, 1920×1080

- Anzahl der replizierten Algorithmus-Kerne: 4

- Verarbeitungsgeschwindigkeit: 120 Bilder pro Sekunde

Lösungskonzept

- Beschleunigerkarte: HES-US-440

- Schnittstelle zur Host-Workstation: HES Proto-AXI

- HES-Utility-Software: HES.Asic.Proto mit PCie-Treiber und Software-API

- RTL-Code des ViBe-Algorithmus

- C++-Code des Hauptprogramms auf der PC-Host-Workstation

Plattform-Dokumentation

Verschlüsselung & Sicherheit

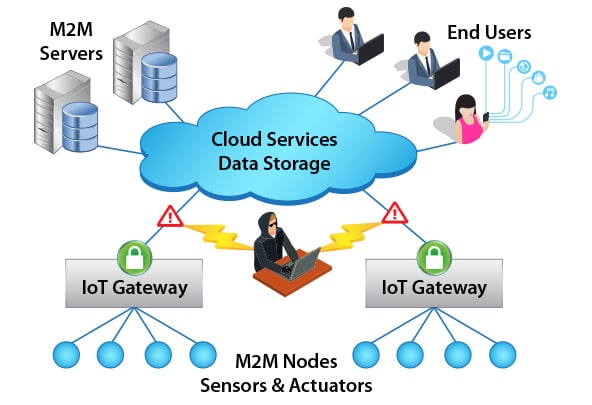

Ver- und Entschlüsselungs-Algorithmen werden in vielen Bereichen eingesetzt, in denen die Sicherheit der übertragenen Daten erforderlich ist. Sie gewährleisten die Sicherheit von Einzelpersonen, Gruppen und Ländern. Neue kryptografische Algorithmen wie AES und DES sind immer rechenintensiver.

Sicherheit ist zu einem der kritischen Faktoren bei eingebetteten Designs geworden, insbesondere bei Anwendungen des Internet-of-Things (IoT) oder der Industrie 4.0. Sensible Telemetriedaten werden vom Einsatzort zur weiteren Verarbeitung in die Cloud gesendet. Aufgrund der Umgebungsbedingungen und der Mobilität werden häufig drahtlose Kanäle verwendet, die jedoch wesentlich anfälliger für Hackerangriffe sind. Daher sollte das Gateway-Gerät, das die Daten sammelt und an die Cloud überträgt, Verschlüsselungs- und Entschlüsselungsalgorithmen bereitstellen.

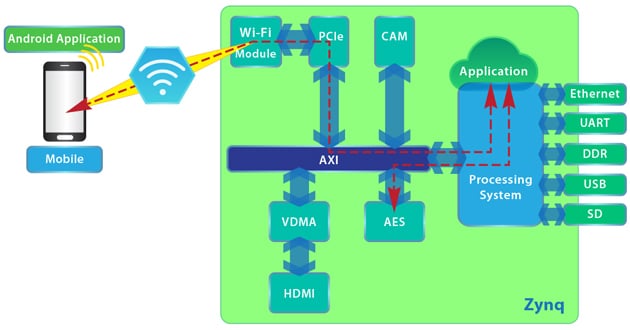

FPGAs, die in das Verarbeitungssystem integriert sind, wie z. B. Xilinx Zynq-Geräte, sind eine geeignete Plattform für die Implementierung von Hardware-Beschleunigern für kryptografische Algorithmen, die zusätzlich angepasst werden können (und somit sicherer sind) und den eingebetteten Prozessor nicht überlasten, der frei ist, um gleichzeitig andere Programme auszuführen. Basierend auf Zynq-Bausteinen bietet Aldec die TySOM-Produktlinie für Embedded-Anwendungen einschließlich Embedded HPC an.

Um die Leistungsfähigkeit von FPGAs in der Kryptographie und in IoT-Anwendungen zu demonstrieren, haben Aldec ein Demo-Design eines Gateway-Geräts erstellt, bei dem der AES-Verschlüsselungsalgorithmus im FPGA implementiert ist und zur Sicherung der über die WiFi-Schnittstelle nach außen übertragenen Daten verwendet wird. Die von verschiedenen Sensoren gesammelten und vom ARM Processing System aggregierten Daten werden dann mit AES verschlüsselt, bevor sie über die WiFi-Schnittstelle übertragen werden. Das empfangende Gerät kann die Daten dann mit dem lokal gespeicherten privaten Schlüssel entschlüsseln. Diese Demo kann als Referenzdesign und als Grundlage für weitere Anpassungen und Implementierungen verwendet werden.

Wichtigste Funktionen

- Referenzdesign eines IoT-Gateways mit Datenverschlüsselung

- Hardware-Implementierung des AES-Verschlüsselungsalgorithmus

- Hauptanwendung läuft in eingebetteter Linux-Umgebung

- Demonstriert die Verwendung von ARM Processing System mit FPGA zur Beschleunigung in einem Chip

- Bietet Optionen zum Anschluss von Edge-Geräten (Sensoren und Aktoren), die mit verschiedenen Standards kommunizieren: Bluetooth, Z-Wave, ZigBee, USB

Lösungskonzept

- Hardware-Plattform: TySOM-1 – Board mit Xilinx Zynq-7000 Baustein

- AES-Beschleuniger-RTL-Code

- Gateway-Embedded-Design-Referenzimplementierung – Hardware und Software

- Eingebettetes Linux, Debian linaro-jessie-alip

- Plattform-Dokumentation

Genom Abgleich

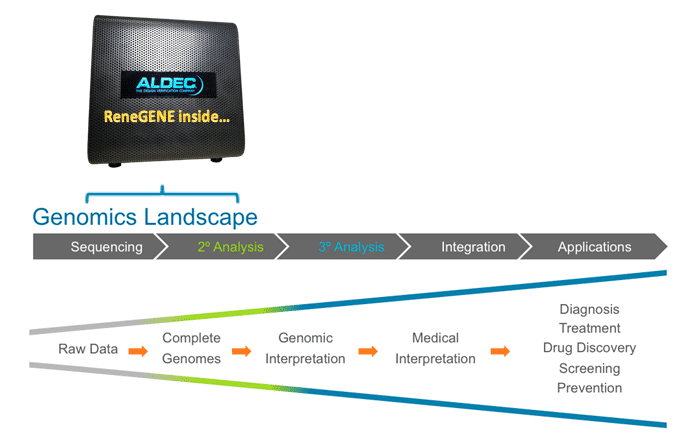

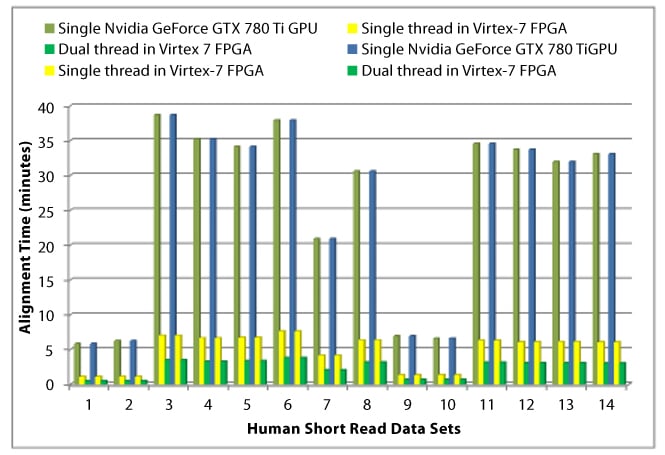

Wissenschaftliche Forschungen in vielen Bereichen benötigen Rechenleistung, manchmal sogar mehr als industrielle Anwendungen. Um die Leistungsfähigkeit von FPGAs zu demonstrieren, haben Aldec und das Fakultätsunternehmen des Indian Institute of Science, ReneLife, den Algorithmus von ReneGENE für ein genaues Genom-Alignment auf dem FPGA-basierten Beschleuniger HES-HPC von Aldec implementiert.

ReneGENE wird auf dem HES-HPC als AccuRA angeboten und ermöglicht ein genaues und ultraschnelles Big Data Mapping und Alignment von DNA-Kurzstreifendaten aus Next Generation Sequencing (NGS)-Plattformen mit vollständiger Abdeckung des Genoms (Millionen bis Milliarden Basen), einschließlich Wiederholungsregionen. Die Technologie, die ohne Heuristiken auskommt, kann die DNA-Lesungen präzise mit einem Referenzgenom mit einer Auflösung von einem Nukleotid abgleichen. Da die Genomik die gesamte Biologie, einschließlich Biomedizin und Therapeutika, durchdringt, schafft ReneGENE eine genomische Autobahn, die erheblich dazu beiträgt, die Zeit von der Probe bis zur Information zu verkürzen, ohne Kompromisse bei der Genauigkeit einzugehen, die für lebensrettende medizinische Anwendungen, biotechnologische Produktentwicklung und Forensik entscheidend ist.

- Aldec HES-HPC ist ~10x schneller als GMAccS, der Single GPU OpenCL

- Aldec HES-HPC ist ~26x schneller als CUSHAW, der Open Source Single GPU CUDA

- GMAccS zeigt eine über 150-fache Beschleunigung im Vergleich zu heuristischen Standard-Alignern wie BFAST, so dass AccuRA um mehrere Größenordnungen schneller ist als die Konkurrenz.

- HES-HPC verfügt über mehr verfügbare FPGA-Ressourcen für mehr Hardware-Kernel, es können bis zu 6 Kernel in einem FPG untergebracht werden

Wichtigste Funktionen

- Vollständiges Streaming, Multithreading, parallele dynamische Programmierung in Hardware beseitigt Speicherengpässe und Speicherprobleme

- Reduziert den Rechen- und E/A-Aufwand auf dem Host erheblich

- Erzielt kurze Lesezuordnungen in minimaler deterministischer Zeit

- Äußerst genaue und präzise SRM-Lösung

- Schnellster Genom-Aligner auf dem Markt

- Skalierbar auf mehreren Ebenen der Design-Granularität, massiv parallele Lösung

- Skalierbar in der Datengröße, von Genomgrößen von Millionen bis Milliarden

- ReneGENE AccuRA ist die kostengünstigste Lösung. Der Kunde wird weniger als ein Prozent seiner monatlichen Ausgaben für die ReneLife-Aldec-Lösung im Vergleich zu konventionellen Clustern aufwenden müssen und spart zudem Zeit durch die beschleunigte Leistung.

- Die Ergebnisse des Alignments von ReneGENE liegen in einem Standardformat vor, das als .SAM oder als äquivalentes Binärformat .BAM bezeichnet wird und von den nachgeschalteten Analysetools in jedem Labor weltweit verarbeitet werden kann.

- Zu den Endnutzern gehören: NGS-OEMs, Große Forschungsgruppen, Medizinische Forschungsgruppen und Krankenhäuser, Kleine Forschungsgruppen und Diagnostiklabors, Forensik, Klinisches Personal

Lösungskonzept

- ReneGENE-Software-Anwendung

- AccuRA-System läuft auf HES-HPC

Hochfrequenzhandel

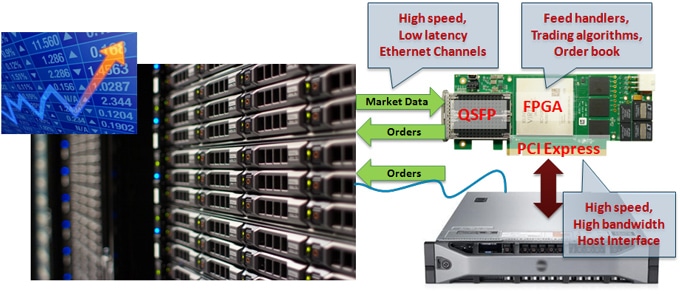

Die Beliebtheit und der Wert von FPGAs für Hochfrequenzhandelssysteme (HFT) haben in den letzten fünf Jahren zugenommen – und der Hauptgrund dafür ist die Latenzzeit. Um wettbewerbsfähig zu bleiben, müssen HFT-Firmen die neuesten Technologien einsetzen, um eine Latenzzeit von nahezu Null zu erreichen – wer das schnellste System hat, gewinnt.

FPGAs bestehen aus Millionen von Logikgattern, die Daten parallel verarbeiten können, im Gegensatz zu Software, die Daten sequentiell ausführt. Daher können FPGAs eine Latenzzeit im Submikrosekundenbereich bieten, verglichen mit mehreren Mikrosekunden bei Software. FPGAs enthalten Tausende von DSP-Blöcken, die mathematische Berechnungen parallel ausführen können, und FPGAs sind auch reprogrammierbar, was flexible Systeme ermöglicht, die sogar im Feld optimiert werden können.

Mit Aldecs über 30-jähriger Erfahrung im Bereich FPGA/ASIC-Prototyping und -Beschleunigung bietet Aldec FPGA-Beschleuniger mit PCIe- und QSFP-Schnittstellen an, die mit 1U- (oder größeren) Handelssystemen für zeitkritische Handelsstrategien wie Market Making, statistische Arbitrage und algorithmischen Handel kompatibel sind.

Erreichen einer niedrigen Latenz

Niedrige Latenzzeiten, die die wichtigste Anforderung sind, wurden durch den Einsatz der neuesten Generation von Xilinx FPGA – Virtex™ UltraScale+ – und den Anschluss aller kritischen Schnittstellen wie Ethernet/QSFP und PCI Express direkt an das FPGA erreicht. Marktdaten, die direkt von der Netzwerkschnittstelle (QSFP) erfasst werden, werden sofort innerhalb der FPGA-Fabric verarbeitet, die Hunderte von parallelen Prozessoren aufnehmen kann, die auf eine bestimmte Aufgabe spezialisiert sind. Die zweite QSFP-Verbindung kann genutzt werden, um Kauf-, Verkaufs- oder Stornierungsaufträge auf der Grundlage der Ergebnisse eines vollständig im FPGA laufenden Algorithmus auszulösen. Alternativ können die vorverarbeiteten Daten über die PCIe-Schnittstelle auf die Host-Workstation übertragen werden, wo sie in der vorhandenen Software analysiert werden. Die Pipelining-Funktionen des FPGA ermöglichen den parallelen Betrieb aller Schnittstellen.

On-the-fly-Neukonfiguration

Das FPGA kann on-the-fly umkonfiguriert werden, ohne dass das gesamte System heruntergefahren werden muss, was die Flexibilität einer solchen Konfiguration erheblich erhöht und eine schnelle Reaktion auf sich dynamisch verändernde Handelsbedingungen erleichtert. Die neuen FPGA-Beschleuniger sind mit 1U und größeren Handelssystemen für zeitkritische Handelsstrategien kompatibel.

FPGA-Designs entwickeln und debuggen

Kunden, die ein komplettes FPGA-Entwicklungs-Ökosystem suchen, profitieren von der Zusammenarbeit mit Aldec mit seinen FPGA-Beschleunigerkarten und RTL-Entwicklungs-/Simulationswerkzeugen wie Riviera-PRO – einem leistungsstarken Mixed-Language-Simulator (VHDL/Verilog/SystemVerilog/SystemC) mit Python-Testbench-Unterstützung für FPGAs.

Integration mit IP-Partnern, die IP-Kerne bereitstellen, die für die Implementierung von Marktdaten-Feed-Handlern und anderen Blöcken des Handelssystems entscheidend sind.

Wichtigste Funktionen

- Schnelle Verarbeitung im neuesten Xilinx UltraScale+ FPGA

- Höherer Speed-Grade (-2) des verwendeten FPGAs

- Schnittstellen mit niedriger Latenz QSFP28

- Host-Schnittstelle mit hoher Bandbreite PCI Express 16x, gen3

Schnelle QDR-II-Speicher - Low-Profile-Boards (können in 1U-Rack-Servern verwendet werden)

- Hot-Rekonfiguration (FPGA-Wechsel ohne Abschalten & PCIe-Link aktiv)

- Lösungsanbieter mit FPGA-Design-Know-how

Lösungskonzept

- FPGA-Board, niedriges Profil, PCIe, Schnittstellen mit geringer Latenz, unterstützt 1U-Rack-Server

- Riviera-PRO Hochleistungssimulator für die Algorithmenentwicklung in HDL

- IP-Partner für Ethernet mit niedriger Latenzzeit

- Referenz- und Diagnose-Designs mit QSFP- und PCIe-Schnittstellen und QDR-II-Speicher-Controlle

Large Scale HPC

Die FPGA-Beschleunigung ist eine wichtige Voraussetzung für die Lösung aktueller Berechnungsprobleme. Neuronale Netze, Deep Learning, Data Mining, Cloud Computing oder wissenschaftliche Forschung sind nur einige der Bereiche, in denen herkömmliche Server trotz ihres hohen Energieverbrauchs nicht genügend Rechenleistung bieten. Die jüngsten, enormen Fortschritte in der FPGA-Technologie haben die Tür für deren Einsatz in HPC-Anwendungen geöffnet.

Die skalierbaren FPGA-Beschleuniger von Aldec sind ideal für groß angelegte HPC-Anwendungen. Die heutige Generation von FPGA-Beschleunigerkarten ist mit stromsparenden Xilinx® Ultrascale™ FPGAs ausgestattet, die herausragende Rechenkapazitäten mit einer Energieeffizienz bieten, die mit GPU-basierten Beschleunigern nicht erreicht werden kann.

FPGA-Beschleuniger

HES-XCVU9P-QDR – Low-Profile-Formfaktor-Board mit PCIe x16, das direkt in Servern in Rechenzentren installiert werden kann. Auf diesem Board ist das FPGA mit QDR-II+-Speichern mit hoher Bandbreite gekoppelt, die einen hohen Durchsatz für die Algorithmusbeschleunigung bieten.

HES-XCVU9P-ZU7EV – Board mit separatem Host-Interface-Chip Xilinx Zynq UltraScale+ XCZU7 und einem weiteren FPGA Xilinx UltraScale+ XCVU9P, der ausschließlich für die Anwendung des Benutzers bestimmt ist. Seine logischen Ressourcen enthalten eine große Anzahl von DSP-Blöcken (6840), wodurch er sich ideal für DSP- und Computer-Vision-Anwendungen eignet.

HES-US-440 – eigenständiges Board mit externem PCIe x8-Kabelanschluss enthält den größten Xilinx Virtex Ultrascale-Baustein mit einer beispiellosen Kapazität von 5,5 Millionen Logikzellen, DDR4-Speicher mit bis zu 64 GB in zwei Modulen und schnellem RLDRAM. Er eignet sich für die Beschleunigung sehr komplexer Algorithmen oder solcher, die von einer großen Anzahl replizierter Instanzen des Algorithmuskerns profitieren können.

HES-XCKU11P-DDR4 – Low-Profile-Formfaktor-Karte mit PCIe x16, die direkt in Servern für HPC/HFT installiert werden kann. Enthält Kintex UltraScale+, das zur FPGA-Familie mit dem besten Preis/Leistungs/Watt-Verhältnis gehört. Zwei QSFP-DD bieten hohe Bandbreite und niedrige Latenz (bis zu 400 Gbps).

| HES-XCVU9P-QDR | HES-XCVU9P-ZU7EV | HES-US-440 | HES-XCKU11P-DDR4 | |

|---|---|---|---|---|

| Logic Cells | 2.5 Million | 2.5 Million | 5.5 Million | 653,000 |

| DSP Blocks | 6840 | 6840 | 2880 | 2,928 |

| On-chip RAM | 75.9 Mb BlockRAM 270 Mb UltraRAM | 75.9 Mb BlockRAM 270 Mb UltraRAM | 88.6 Mb BlockRAM | 21.1 Mb BlockRAM 22.5 Mb UltraRAM |

| Off-chip RAM | 432 Mb QDR-II (3x 144 Mb) Or in *-DDR version: 32 Gb DDR4 (2x 16Gb) 144 Mb QDR-II | 32GB DDR4 (2x 16GB) 2x 576Mb RLD3 | 32GB DDR4 (2x 16GB) 1152 Mb RLD3 (2x 576Mb) | SODIMM DDR4 Memory socket 512 Mb Flash Memory 2x 64 kb I2C EEPROM |

| Host Interface | PCI Express x16, gen3 | PCI Express x8, gen3 Zynq UltraScale+ XCZU7 | PCI Express x8, gen2 Zynq-7000, XC7Z100 | PCIe x16 gen3 endpoint or PCIe x8 gen4 2x QSFP-DD (total up to 400Gbps) |

Host-Schnittstelle

Die Verbindung der FPGA-Beschleunigerkarte mit einer Host-Workstation über PCIe ist nicht trivial und würde, wenn sie von Grund auf durchgeführt würde, umfangreiche Kenntnisse im Hardware-Design erfordern. Software-Entwickler benötigen eine einsatzbereite Hardware-Plattform, die keine Auswirkungen auf die Low-Level-Hardware-Integration hat. Aldec hat ein solches Anwendungsmodell verstanden und bietet die HES Proto-AXI-Schnittstelle an, die die Details der PCI-Express-Implementierung auf niedriger Ebene verbirgt und Ihre Entwicklungszeit spart. Der Anwender erhält den HES Proto-AXI IP-Kern, der auf dem AMBA AXI-Standard basiert und beschleunigte Algorithmus-Kernel mit dem PCIe-Bus des Host-Computers verbindet.

Die skalierbaren FPGA-Beschleuniger von Aldec sind ideal für groß angelegte HPC-Anwendungen. Die heutige Generation von FPGA-Beschleunigerkarten ist mit stromsparenden Xilinx® Ultrascale™ FPGAs ausgestattet, die herausragende Rechenkapazitäten mit einer Energieeffizienz bieten, die mit GPU-basierten Beschleunigern nicht erreicht werden kann.

FPGA-Beschleuniger

HES-XCVU9P-QDR – Low-Profile-Formfaktor-Board mit PCIe x16, das direkt in Servern in Rechenzentren installiert werden kann. Auf diesem Board ist das FPGA mit QDR-II+-Speichern mit hoher Bandbreite gekoppelt, die einen hohen Durchsatz für die Algorithmusbeschleunigung bieten.

HES-XCVU9P-ZU7EV – Board mit separatem Host-Interface-Chip Xilinx Zynq UltraScale+ XCZU7 und einem weiteren FPGA Xilinx UltraScale+ XCVU9P, der ausschließlich für die Anwendung des Benutzers bestimmt ist. Seine logischen Ressourcen enthalten eine große Anzahl von DSP-Blöcken (6840), wodurch er sich ideal für DSP- und Computer-Vision-Anwendungen eignet.

HES-US-440 – eigenständiges Board mit externem PCIe x8-Kabelanschluss enthält den größten Xilinx Virtex Ultrascale-Baustein mit einer beispiellosen Kapazität von 5,5 Millionen Logikzellen, DDR4-Speicher mit bis zu 64 GB in zwei Modulen und schnellem RLDRAM. Er eignet sich für die Beschleunigung sehr komplexer Algorithmen oder solcher, die von einer großen Anzahl replizierter Instanzen des Algorithmuskerns profitieren können.

HES-XCKU11P-DDR4 – Low-Profile-Formfaktor-Karte mit PCIe x16, die direkt in Servern für HPC/HFT installiert werden kann. Enthält Kintex UltraScale+, das zur FPGA-Familie mit dem besten Preis/Leistungs/Watt-Verhältnis gehört. Zwei QSFP-DD bieten hohe Bandbreite und niedrige Latenz (bis zu 400 Gbps).

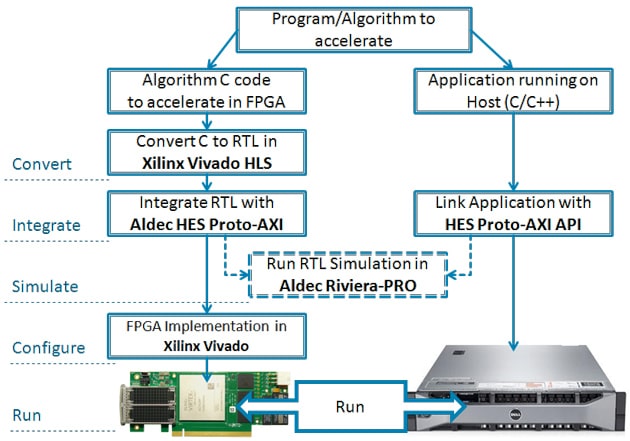

Konvertieren

Das zu beschleunigende Programm oder der Algorithmus wird in zwei Teile aufgeteilt – einen, der für die Beschleunigung bestimmt ist, und den anderen, der auf dem Host läuft. Eine solche Partitionierung kann auf der Grundlage der Ergebnisse der Profilerstellung erfolgen, die auf rechenintensive Teile des C-Codes hinweisen. Anschließend wird das Xilinx Vivado HLS-Tool zur Konvertierung von C in Verilog- oder VHDL-RTL-Code verwendet, der für die weitere automatische Verarbeitung (Synthese und Implementierung in FPGA) geeignet ist. Der Benutzer sollte sich dafür entscheiden, die AMBA AXI-Schnittstelle in den RTL-Code einzubinden, die für den nächsten Schritt benötigt wird.

Einbinden

Sobald der HDL-Code verfügbar ist, muss er in Aldec HES Proto-AXI integriert werden – das heißt, er muss mit den AMBA AXI-Ports verbunden werden. Die Verwendung eines HDL-Editors, wie z. B. Riviera-PRO von Aldec, ist für diesen Schritt ausreichend. Gleichzeitig wird die Hauptanwendung, die auf dem Host-Computer laufen soll, so modifiziert, dass die Aufrufe der Algorithmusfunktionen durch ihre Gegenstücke auf dem FPGA über die HES Proto-AXI API ersetzt werden.

Simulieren

Bevor Sie das gesamte Projekt mit der FPGA-Beschleunigerkarte ausführen, können Sie es mit dem Hochleistungssimulator Riviera-PRO von Aldec und dem HES Proto-AXI-Simulationsmodell, das in der Large Scale HPC-Lösung enthalten ist, auf etwaige Integrations-/Anschlussfehler überprüfen.

Konfigurieren Sie

Der letzte Schritt ist die automatische Synthese und Implementierung mit der Xilinx Vivado-Umgebung, die FPGA-Bitströme und Konfigurationsdateien für Ihre Hauptanwendung erzeugt.

Ausführen

Aldec bietet eine Laufzeitumgebung, die die Nutzung von FPGA-Beschleunigerkarten einfach macht. Der PCI-Express-Gerätetreiber ist installiert und die Housekeeping-Funktionen des Accelerator Boards sind in der Proto-AXI-API-Bibliothek enthalten, die mit Ihrem Programm verknüpft ist. Wenn Sie Ihre Hauptanwendung auf dem Host-Computer starten, wird das FPGA automatisch konfiguriert, so dass keine speziellen Kenntnisse über den FPGA-Betrieb oder die Programmierung erforderlich sind, was eine sehr komfortable Umgebung für Software-Entwickler darstellt.

Wichtigste Funktionen

- Auswahl verschiedener FPGA-Beschleunigerkarten zur Anpassung an die Projektanforderungen

- Skalierbarkeit durch Unterstützung mehrerer Board-Konfigurationen

- Unterstützt Hot-Rekonfiguration von FPGA

- Integriert in FPGA-Entwicklungs- und Verifikationsumgebung

Lösungskonzept

- HES-HPC FPGA-Beschleunigerkarte

- HES Proto-AXI Host-Schnittstellenmodul und Software-Stack

- AXI-Bus-Funktionsmodell (BFM) für die RTL-Simulation

- Riviera-PRO-Hochleistungs-HDL-Simulator

- Referenzdesigns, technische Dokumentation, Tutorials und White Papers

- Integrationsdienstleistungen

Embedded HPC

In den letzten Jahren gab es einen regelrechten Ansturm auf Embedded-Elektronik, von denen viele sehr leistungsfähige Mikroprozessoren enthalten, die die Fähigkeiten der vor zehn Jahren verfügbaren Desktop-Computer übertreffen. Smartphones sind ein weit verbreitetes Beispiel, aber es gibt Hunderte von anderen. Computer Vision, Automobilsysteme, UAV (Drohnen), Sicherheitskameras und Netzwerksicherheit sind nur einige Kategorien, in denen eingebettete Elektronik zum Einsatz kommt.

Der Embedded HPC ist die Antwort auf den wachsenden Bedarf an Rechenleistung in eingebetteten Anwendungen. Für diese Art von Anwendungen müssen CPU und FPGA auf demselben Board und idealerweise im selben Chip untergebracht sein. Aus diesem Grund basieren die TySOM-Boards von Aldec auf der Xilinx Zynq-Familie von MPSoC und Chipsätzen, die ARM Programmable System und FPGA integrieren.

TySOM-3A-ZU19EG ist ein kompaktes SoC-Prototyping-Board mit Zynq® UltraScale+™ MPSoC-Baustein, der 64-Bit-Prozessor-Skalierbarkeit bietet und Echtzeitsteuerung mit Soft- und Hard-Engines für SoC-Prototyping-Lösungen, IP-Verifikation, Grafik, Video, Paketverarbeitung und frühe Softwareentwicklung kombiniert. Der Hauptvorteil des Xilinx Zynq Ultrascale+ ZU19EG-FFVB1517 MPSoC gegenüber anderen Zynq MPSoC-Bausteinen besteht darin, dass er das größte FPGA der Zynq® UltraScale+™ MPSoC-Familie mit über einer Million Logikzellen enthält. Er enthält eine Quad-Core ARM® Cortex-A53 Plattform, die mit bis zu 1,5 GHz läuft. Kombiniert mit Dual-Core Cortex-R5 Echtzeitprozessoren, einer Mali-400 MP2 Grafikeinheit und 16nm FinFET+ 1.143K Logikzellen in der programmierbaren Logik. Dieses Prototyping-Board enthält 8 GB DDR4-Speicher für die programmierbare Logik (PL) und ebenfalls 8 GB DDR4-SODIMM-Speicher für das Verarbeitungssystem (PS). Dieses Board enthält 2 Gb NAND-Speicher und unterstützt bis zu 32 GB SSD-Speicher auf einer Micro-SD-Karte. Außerdem verfügt es über einen 512Mb QSPI-Flash-Speicher. Die Kommunikation und Vernetzung wird durch ×2 Gigabit Ethernet, Wi-Fi & Bluetooth, CAN, Pmod, 4× USB 3.0, USB to UART Bridge, USB 2.0 OTG, JTAG USB, SATA, QSFP+ und PCIe x1 GEN3/4 Anschlüsse ermöglicht. Multimedia-Schnittstellen werden über DisplayPort und HDMI IN/OUT bereitgestellt. Zur Erweiterung der Peripherie sind 2× FMC VITA 57.1-2010 konform auf dem Board vorhanden. So können zusätzliche Geräte als FMC-Tochterkarten, die von Aldec angeboten werden, angeschlossen werden.

TySOM-3-ZU7 – Beschleuniger-Board basierend auf Zynq UltraScale+ ZU7EV mit FPGA mit Quad-Core ARM Cortex-A53 Universalprozessor, ARM Cortex-R5 Echtzeitprozessor, ARM Mali-400 Grafikprozessor und H.264/H.265 Video-Codec. Das eingebettete FPGA kann zur Beschleunigung der kritischsten Funktionen der eingebetteten Anwendung oder zur Implementierung der Klebelogik für die Schnittstellen externer Geräte verwendet werden. Die heterogene Architektur von ZU7EV ist eine leistungsstarke Plattform für verschiedene Anwendungen wie neuronale Netzwerke, Verschlüsselung oder Bild- und Videoverarbeitung.

TySOM-2 – Beschleunigerkarte auf Basis des Zynq-7000 XC7Z100 mit Dual-Core ARM Cortex-A9 Universalprozessor in einem Chip und dem größten FPGA der Zynq-7000 Familie. Die große Anzahl von DSP-Blöcken (2020) macht es perfekt für Embedded-Vision-Anwendungen.

Entwurfsautomatisierung

Zur Erleichterung des Entwurfs eingebetteter HPC-Anwendungen bietet Aldec TySOM-Systemplattformen an, die in das Xilinx SDx-Tool geladen werden können. In SDx werden dann C/C++ Algorithmus-Dateien kompiliert und in einen für FPGAs geeigneten RTL-Code umgewandelt. Schließlich wird der RTL-Code automatisch mit der ausgewählten Systemplattform verbunden.

Wenn alle Kompilierungs- und Implementierungsschritte abgeschlossen sind, ist die Ausführung der eingebetteten Anwendung so einfach wie das Hochladen der von SDx generierten Dateien auf die SD-Karte und das Starten der Ausführung im TySOM-Board.

Referenzdesigns und Dienstleistungen

Für einen schnellen Start bietet Aldec mehrere Referenzdesigns an, die den Einsatz verschiedener Peripheriegeräte und programmierbarer Logik (FPGA) zur Beschleunigung von Anwendungsalgorithmen und zur funktionierenden Implementierung von Embedded Linux demonstrieren. Wenn Sie die Vorteile von FPGA-gestütztem eingebettetem HPC erkannt haben, es Ihrer Organisation aber an Hardware-Design-Know-how mangelt, können die kundenspezifischen Engineering-Services von Aldec diese Lücke schließen. Unsere langjährige Erfahrung im FPGA-Hardwaredesign und in der Verifikation kann effektiv genutzt werden, um schnell ein komplettes System zu erstellen oder Ihre Algorithmen mit Referenzdesigns zu integrieren, die sofort verfügbar sind.

Wichtigste Funktionen

- Portfolio von TySOM-Boards für verschiedene Anforderungen

- Kompatibel mit ergänzenden FMC-Tochterkarten

- Vollständige Design- und Verifikationsumgebung

- Enge Integration mit Xilinx SDx und Vivado Software

- Hochwertige und solide Hardware

Lösungskonzept

- Aldec TySOM-Platine

- TySOM-Referenzdesigns im Paket

- Riviera-PRO HDL-Simulator (optional)

- Technische Dokumentation, Tutorials und White Papers

- SDx-Hardware-Plattformpaket (Board Support Package – BSP)

- Kundenspezifische Entwicklung für RTL Porting Services