FPGA Simulation

Functional Verification

Emulation & Prototyping

Requirement Management

Mil/Aero Verification

Aldec, Inc.

Aldec, Inc. ist ein führender Electronic Design Automation Hersteller der sich auf die Entwicklung von Software, für die Verifikation komplexer FPGA, ASIC und SoC, spezialisiert hat. Die Qualität der Produkte und der kundenorientierte Support zeichnen Aldec besonders aus. Eine aktive Benutzergemeinde (nach ALDEC Angaben über 35.000! Anwender) hat sich bereits für das Aldec Portefeuille entschieden.

Wesentliche Schritte zur Vereinfachung von VHDL-Testbenches mit OSVVM

Dieses Webinar zum Thema „Erste Schritte“ konzentriert sich auf die ersten, wesentlichen Schritte, die Sie unternehmen müssen, wenn Sie Ihren VHDL-Testbench-Ansatz mit OSVVM verbessern wollen.

Überprüfung von AXI-Verbindungen mit ALINT-PRO und Riviera-PRO

AXI ist das beliebteste interne Busprotokoll bei den heutigen FPGA- und SoC-FPGA-Designs geworden. Mit ALINT-PRO können FPGA-Designer AXI-Busschnittstellen extrahieren, überprüfen und statisch verifizieren. Darüber hinaus kann ALINT-PRO bei der automatischen...

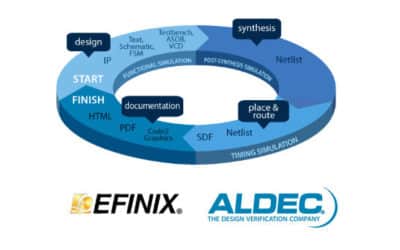

Effinix und Aldec Active-HDL Promoaktion

Active-HDL Designer Edition Perpetual Lizenz – Fordern Sie ein Angebot an! Active-HDL™ ist eine Windows®-basierte, integrierte FPGA-Design-Erstellungs- und Simulationslösung für teambasierte Entwicklungsumgebungen.

Riviera-PRO unterstützt OpenCPI für heterogenes Embedded Computing

Aldec unterstützt mit der neuesten Version von Riviera-PRO (Version 2022.04) die Open Component Portability Infrastructure (OpenCPI).

FPGA Verifizierung Code- Funktions- und Spezifikationsabdeckung

Functional Coverage wird oft zusammen mit der FPGA Verifikation nach dem Zufallsprinzip erwähnt, und das ist eine großartige Kombination.

Randomization – Das Warum, Wann, Was und Wie

Randomization ist für die moderne Verifikation sehr wichtig. Dennoch wenden nur sehr wenige Entwickler die Randomization in ihren Testbenches ausreichend an.

FPGA-Verifikationsarchitektur-Optimierung mit UVVM

Wie Sie mit der Open-Source-Architektur der Universal VHDL Verification Methodology (UVVM) eine einfache, gut strukturierte und effiziente Testbench erstellen können

Optimierung der FPGA-Entwurfsarchitektur

Die FPGA-Entwurfsarchitektur ist der wichtigste und primäre Faktor, wenn es darum geht, Entwicklungseffizienz, Qualität und Zuverlässigkeit zu erreichen. Der Unterschied zwischen einer guten und einer schlechten Design-Architektur kann etwa 50 % des Arbeitsaufwands ausmachen.

Verbesserung der Verifikationsmöglichkeiten von VHDL mit VHDL-2019 Protected Types

Die neueste Version von Aldec’s Active-HDL unterstützt IEEE 1076-2019 protected types und ermöglicht es Ingenieuren, die Konstruktion von Datenstrukturen für die Verifikation zu vereinfachen und zu abstrahieren.

Verwendung von SVA für die anforderungsbasierte Verifikation von sicherheitskritischen FPGA-Designs

Donnerstag 10. März von 15.00 Uhr bis 16.00 UhrDie Requirements-based Verifikation (RBV) ist ein beliebtes Verifikationsverfahren für FPGA-Designs, die in sicherheitskritischen Systemen eingesetzt werden. Die Effektivität der RBV wird durch die Qualität und Präzision...