IDS-Validate™

Automatisierte Pre-Silizium- und Post-Silizium-Validierung

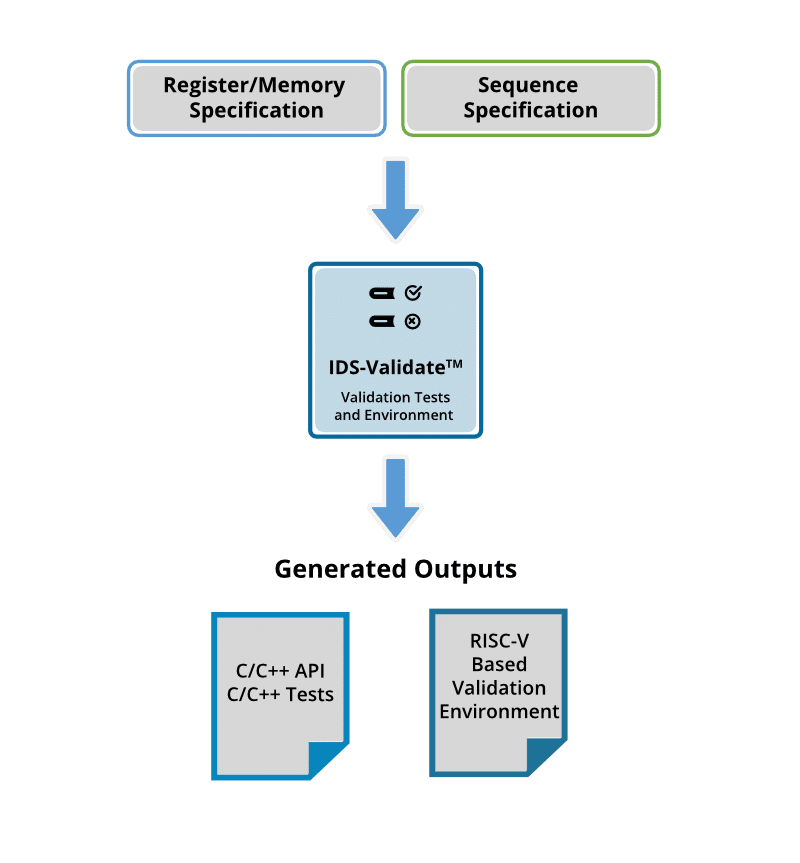

Die Registerverifikationsfunktionen von IDS-Verify werden durch IDS-Validate auf Ihre Pre-Silicon und Post-Silicon Validierung erweitert. IDS-Validate generiert automatisch sowohl UVM- als auch C/C++-Sequenzen, einschließlich benutzerdefinierter Sequenzen, die Ihre Speicher und Register umfassend testen. IDS-Validate geht auch über Register und Speicher hinaus und generiert Verifikationsumgebungen und benutzerdefinierte Funktionstests, um das funktionale Verhalten Ihrer benutzerdefinierten Designblöcke zu verifizieren.

Verkürzung der Verifikations- und Validierungszeit für SoCs

IDS-Validate is the solution for SOC/IP teams who aim to cut down the verification your validation time. The automatic generation of UVM and sequences enables exhaustive testing of memories and register maps.

IDS-Validate also provides a way to generate custom tests for your boards as well as UVM and UVM-C based environments through a common specification. This provides a solution for your firmware engineers to write and debug their device drivers and application software.

Wie IDS-Validate Ihren Entwicklungsprozess verbessert

Automatische Testgenerierung

Aus einer einzigen Spezifikation mit IDesignSpec GDI, Python oder Microsoft Excel können Sie automatisch Tests generieren, die in UVM- und UVM-C/C++-Hybridumgebungen sowie auf physischen Boards laufen. Somit deckt IDS-Validate sowohl die anfängliche Validierung vor dem Silizium (auch bekannt als Hardware-Software-Coverifikation) als auch die abschließende Validierung nach dem Silizium in Ihrem Bring-up-Labor ab.

Die generierten hybriden Umgebungen können sowohl C/C++- als auch UVM-Tests ausführen, die von einer ebenfalls von IDS-Validate generierten Synchronisierungskomponente koordiniert werden. Die Umgebungen sind in der Lage, Interrupts und die dazugehörigen Interrupt-Service-Routinen (ISRs) zu verarbeiten. Sie können die Verbindungen zwischen Ihren Designblöcken testen und die generierte Umgebung als Ausgangspunkt für die Entwicklung einer vollständigen SoC-Verifikationsumgebung verwenden.

Sie können den generierten C/C++-Code auf Ihren eigenen eingebetteten Prozessoren ausführen, oder Sie können einen RISC-V SweRV Core EH1 verwenden, der mit IDS-Validate geliefert wird.

Automatisierung von portablen Sequenzen aus einer Spezifikation

IDS-Validate vereinheitlicht auch die Erstellung von portablen Sequenzen aus einer goldenen Spezifikation. Sie können Sequenzen in Python, im Tabellenkalkulationsformat oder in der Sequenzansicht von IDesignSpec GDI erfassen und mehrere Ausgabeformate für eine Vielzahl von Domänen erzeugen:

- UVM-Sequenzen für die Verifikation

- SystemVerilog-Sequenzen für die Validierung

- C-Code für die Entwicklung von Firmware und Gerätetreibern

- Spezialisierte Formate für automatisierte Testgeräte (ATE)

- Hooks für den neuesten Portable Stimulus Standard (PSS)

- Dokumentationsausgaben wie HTML und Flussdiagramme

Die Sequenzkonstrukte umfassen Schleifen, if-else-, wait- und switch-Anweisungen, um die Schnittstellen zu ändern, Kodierungsformate zu spezifizieren, mit Unterschieden in Zeiteinheiten umzugehen, Makros zu verwenden, Varianten zu spezifizieren und Return-Anweisungen zu verwenden, um Benutzerfehler aus Sequenzen zurückzugeben. Die Konstrukte unterstützen eingeschränkte Variablen für randomisierte Sequenzen und die Handhabung von indirekten und Unterbrechungsregistern.