UVM Register Model Generation

System RDL und IP-XACT Compiler

Automatically generate UVM Sequences

Advanced SoC Verification Tool

Agnisys Inc. – Automatisierung von SOC-, ASIC-, FPGA- und IP-Spezifikation

Sparen Sie wertvolle Projektzeit und Ressourcen durch die automatische Generierung vieler Arten von Design- und Verifikationsdateien aus den technischen Spezifikationen.

Agnisys Inc. hat eine Reihe von Produkten und Lösungen für die Automatisierung von Spezifikationen entwickelt, mit denen die Generierung der erforderlichen Dateien für Design, Software, Verifizierung, Validierung und Dokumentation für die Halbleiterentwicklung direkt aus den ausführbaren Spezifikationen optimiert wird. Dies spart Ihren IP- und Chip-Entwicklungsteams im Laufe eines Projekts mehrfach Zeit und Mühe. Wann immer sich eine Spezifikation aus irgendeinem Grund ändert, werden alle Ausgabedateien aktualisiert, so dass alle Teams auf dem gleichen Stand bleiben.

Agnisys ist damit ein führender Anbieter von Electronic Design Automation Software zur Lösung komplexer Design- und Verifikationsprobleme in der Systementwicklung. Die Produkte bieten einen gemeinsamen, spezifikationsgetriebenen Entwicklungsablauf zur Beschreibung von Registern und Sequenzen für System-on-Chip und IP’s (Intellectual Property), der ein schnelleres Design, eine schnellere Verifikation, Firmware und Validierung ermöglicht. Agnisys hat seinen Hauptsitz in Boston, Massachusetts, und verfügt über F&E-Zentren in den Vereinigten Staaten und Indien.

Die Methodik zur schnelleren Entwicklung besserer Halbleiter

Das Dilemma zwischen Spezifikation und Entwurf

Traditionell gab es keine automatisierte Verbindung zwischen Designspezifikationen und dem Entwicklungsprozess. Die Designer schrieben die RTL-Spezifikation von Hand, die Programmierer für eingebettete Systeme schrieben den C/C++-Code von Hand, und die Verifizierungsteams kodierten Testbenches und Tests – alles auf der Grundlage der gleichen Spezifikation. Natürliche Sprache ist von Natur aus mehrdeutig, so dass verschiedene Teams unterschiedliche Interpretationen hatten. Ein Großteil des Projekts wurde damit verbracht, Fehler aufgrund von Unstimmigkeiten zu beheben.

Auswirkungen von Spezifikationsänderungen

Die Spezifikationen ändern sich im Laufe eines Projekts häufig, und jedes Mal, wenn dies geschah, wurde der Entwicklungsprozess wiederholt. Die Änderungen mussten den einzelnen Teams mitgeteilt werden, die sie interpretierten und ihren Code manuell aktualisierten. Dabei traten unweigerlich neue Unstimmigkeiten auf, was zu einer mühsamen Fehlersuche führte, um die Probleme zu beheben. Die Kosten für den Zeitplan und die Projektressourcen waren enorm.

Ausführbare Spezifikationen sparen Zeit und reduzieren Fehler

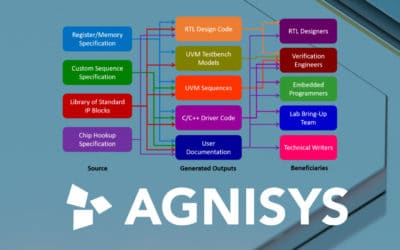

In der Agnisys-Methodik können viele Spezifikationen in ausführbaren Formaten geschrieben werden, aus denen die Agnisys-Tools automatisch Design-, Programmier-, Verifizierungs-, Validierungs- und Dokumentationsdateien generieren können. Jedes Mal, wenn eine Spezifikation geändert wird, werden alle Dateien automatisch neu generiert und die Änderungen eingearbeitet. Dies ersetzt mühsame manuelle Arbeit und sorgt dafür, dass alle Ihre Teams jederzeit auf dem gleichen Stand sind.

Agnisys kündigt Qualifizierung nach ISO 26262 und IEC 61508 für den gesamten Automatisierungsprozess in der SoC-Spezifikation an

Entwickler von sicherheitsrelevante elektrische/elektronische Systeme in Kraftfahrzeugen können nun die Agnisys Lösungen ohne zusätzliche Tool-Qualifizierung einsetzen

Spezifikationsautomatisierung für Entwickler

Anforderungen für verschiedene Projektteams und verschiedene Aufgaben im System-on-Chip (SoC)-Entwicklungsprozess: Hardware-Design, Simulation, formale Verifizierung, Firmware-Codierung, Validierung auf Systemebene und mehr.

Ein hoher Qualitätsstandard für standardbasiertes IP

Die Standard Library of IP Generators (SLIP-G™) hat sich bei den Anwendern als sehr beliebt erwiesen, und das ist nicht überraschend. Die Wiederverwendung spielt bei der Entwicklung von System-on-Chip (SoC) eine große Rolle.

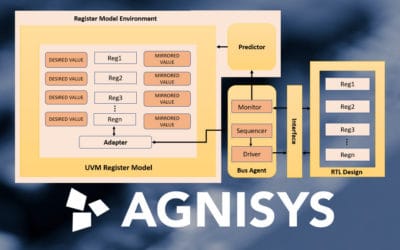

Automatisierung des UVM Register Abstraction Layers (RAL)

Dieser Beitrag konzentriert sich auf den UVM Register Abstraction Layer (RAL), auch UVM Register Layer genannt. Die heutigen großen System-on-Chip (SoC)-Entwürfe enthalten viele Steuer- und Statusregister, auf die oft sowohl von eingebetteter Software oder Treibern als auch von der Hardware aus zugegriffen werden kann

Automatisierung der IP- und SoC-Entwicklung

Agnisys hat seinen ursprünglichen Fokus von der Registerautomatisierung auf spezifikationsgesteuertes Design, Verifikation, Embedded-Programmierung, Validierung und Dokumentation von IPs und SoCs erweitert. Diese Erweiterung ist sowohl ein Beweis für das Wachstum von Agnisys als Unternehmen als auch für die vielen Herausforderungen, denen sich Halbleiter-Entwicklungsteams stellen müssen

Webinar zur Embedded Systementwicklung mit Agnisys

Die Agnisys-Methode zur Entwicklung von Embedded-Produkten. Auf diese Weise lassen sich viele Fallstricke vermeiden, die in einem typischen Workflow auftreten, wie z. B. ein langsamer Prozess, doppelter Aufwand, verschwenderische Ressourcen usw.

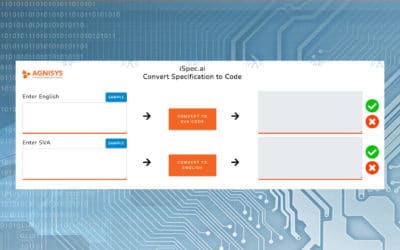

Englische Beschreibung automatisch in SystemVerilog Assertions übersetzen

Agnisys hat einen einzigartigen Ansatz entwickelt, bei dem künstliche Intelligenz (KI) und maschinelles Lernen (ML) eingesetzt werden, um englische Beschreibungen der Entwurfsabsicht in SystemVerilog Assertions (SVA) zu übersetzen.

Ein einheitlicher Entwicklungsablauf für embedded Systeme

Agnisys hat einen einheitlichen Entwicklungsablauf für Embedded Systems definiert, der alles miteinander verzahnt. Sie bieten eine Methodik und Richtlinien dafür, wie und wann die einzelnen Werkzeuge eingesetzt werden, um den größten Nutzeffekt zu erzielen.