eVision Systems Blog

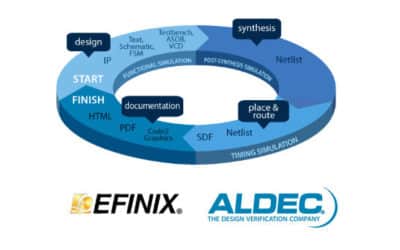

Effinix und Aldec Active-HDL Promoaktion

Active-HDL Designer Edition Perpetual Lizenz – Fordern Sie ein Angebot an! Active-HDL™ ist eine Windows®-basierte, integrierte FPGA-Design-Erstellungs- und Simulationslösung für teambasierte Entwicklungsumgebungen.

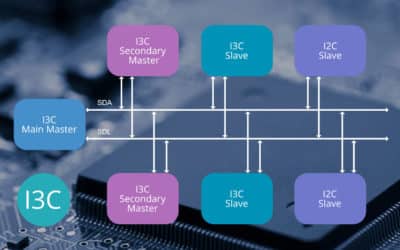

Die 10 größten Probleme bei der Entwicklung mit den I3C Bussystem

Entwickler von Endgeräten und embedded Systeme, speziell für den Einsatz im IoT (Internet of Things), Automotive Bereich und Industrieautomatisierung, sind mit immer höheren Anforderungen an niedrigen Stromverbrauch, Datenbandbreite und Miniaturisierung konfrontiert....

Was ist ein Logikanalysator / Logic analyzer?

Ein Logik-Analysator ist ein elektronisches Messgerät, das mehrere Signale aus einem digitalen Design erfasst und anzeigt. Es ist ein ausgezeichnetes Werkzeug zur Überprüfung und Fehlersuche bei IC`s, digitalen Systemen und digitalen Schaltungen wie z.B. bei embedded...

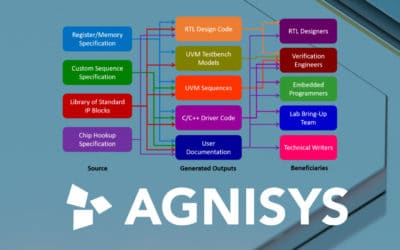

Spezifikationsautomatisierung für Entwickler

Anforderungen für verschiedene Projektteams und verschiedene Aufgaben im System-on-Chip (SoC)-Entwicklungsprozess: Hardware-Design, Simulation, formale Verifizierung, Firmware-Codierung, Validierung auf Systemebene und mehr.

Ein hoher Qualitätsstandard für standardbasiertes IP

Die Standard Library of IP Generators (SLIP-G™) hat sich bei den Anwendern als sehr beliebt erwiesen, und das ist nicht überraschend. Die Wiederverwendung spielt bei der Entwicklung von System-on-Chip (SoC) eine große Rolle.

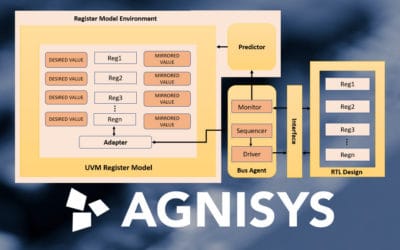

Automatisierung des UVM Register Abstraction Layers (RAL)

Dieser Beitrag konzentriert sich auf den UVM Register Abstraction Layer (RAL), auch UVM Register Layer genannt. Die heutigen großen System-on-Chip (SoC)-Entwürfe enthalten viele Steuer- und Statusregister, auf die oft sowohl von eingebetteter Software oder Treibern als auch von der Hardware aus zugegriffen werden kann

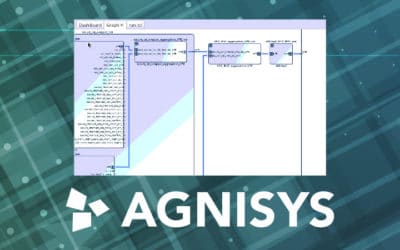

Automatisierung der IP- und SoC-Entwicklung

Agnisys hat seinen ursprünglichen Fokus von der Registerautomatisierung auf spezifikationsgesteuertes Design, Verifikation, Embedded-Programmierung, Validierung und Dokumentation von IPs und SoCs erweitert. Diese Erweiterung ist sowohl ein Beweis für das Wachstum von Agnisys als Unternehmen als auch für die vielen Herausforderungen, denen sich Halbleiter-Entwicklungsteams stellen müssen

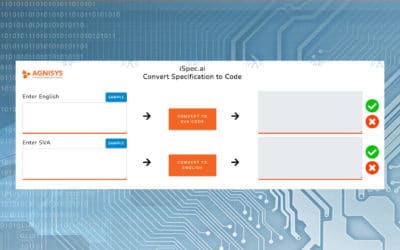

Englische Beschreibung automatisch in SystemVerilog Assertions übersetzen

Agnisys hat einen einzigartigen Ansatz entwickelt, bei dem künstliche Intelligenz (KI) und maschinelles Lernen (ML) eingesetzt werden, um englische Beschreibungen der Entwurfsabsicht in SystemVerilog Assertions (SVA) zu übersetzen.

Ein einheitlicher Entwicklungsablauf für embedded Systeme

Agnisys hat einen einheitlichen Entwicklungsablauf für Embedded Systems definiert, der alles miteinander verzahnt. Sie bieten eine Methodik und Richtlinien dafür, wie und wann die einzelnen Werkzeuge eingesetzt werden, um den größten Nutzeffekt zu erzielen.