Erstellen von HDL Beschreibungen für ASIC und FPGA Designs

Egal ob Sie mit VHDL oder Verilog arbeiten werden Sie feststellen, dass sich Hardwarebeschreibungssprachen von sequenziellen Programmiersprachen unterscheiden, da es sich bei VHDL und Verilog um parallele Sprachen handelt, die für das Modellieren von Hardware spezifiziert wurden. In der Regel besteht der Design Flow in der Hardwareentwicklung für FPGA und ASIC Komponenten aus Eingabe, Simulation, Synthese, Place&Route, Validierung der Chips.

Am Anfang des Entwicklungsprozesses in der Hardwareentwicklung steht die HDL Code Beschreibung. Hier gibt es zunächst verschiedene grundsätzliche Entscheidungen:

- Welche Sprache (VHDL, Verilog, System Verilog, SystemC)?

- Soll es ein einsprachiges Design oder ein gemischtsprachiges Design werden (z.B. VHDL für die eignen Blöcke und Verilog für IP Blocks der FPGA Hersteller)?

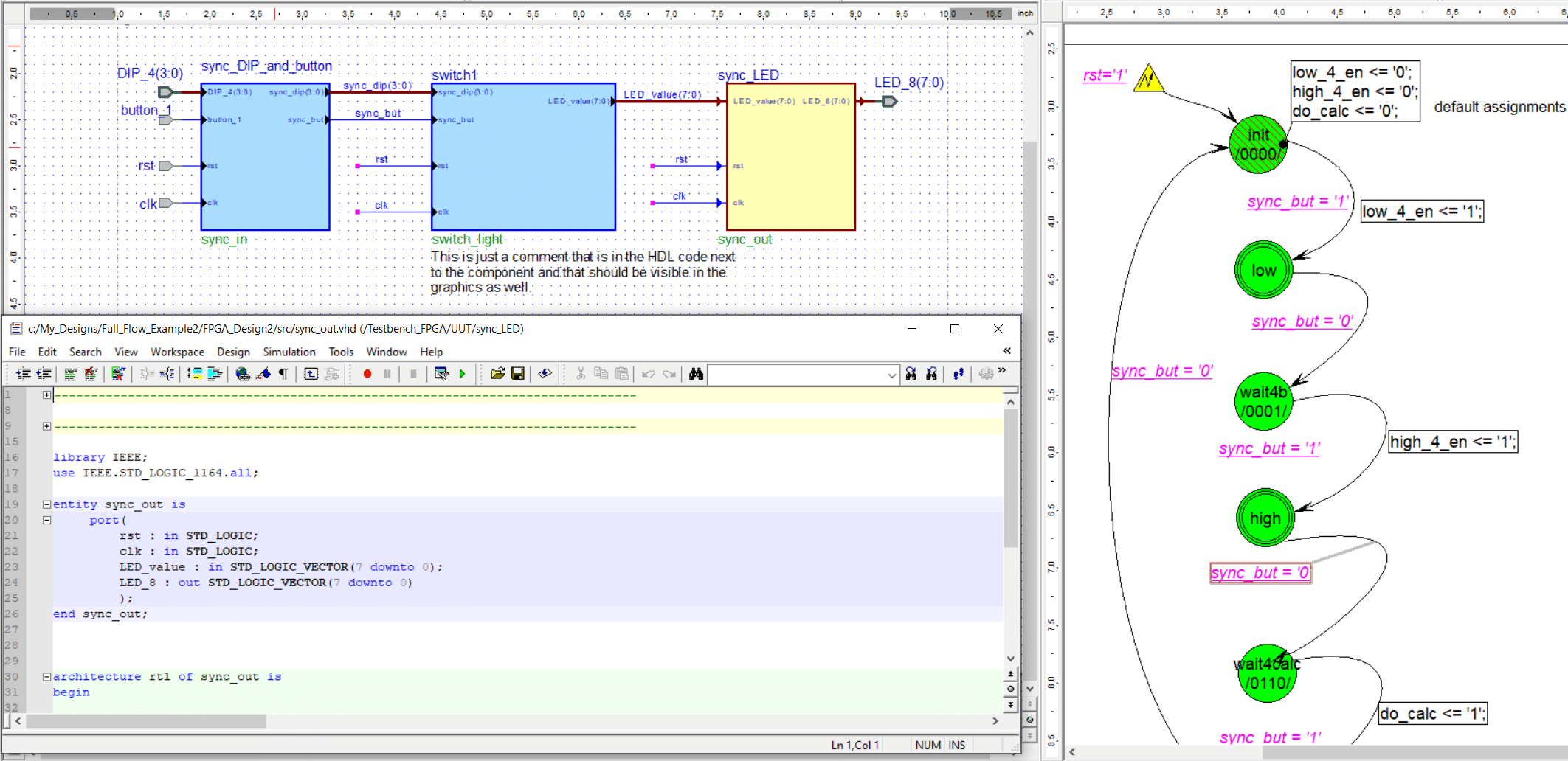

- Werden alle Blöcke textuell beschrieben oder soll auch ein grafisches Tool zum Einsatz kommen?

Bei der Bewertung der Vor- und Nachteile sind wir Ihnen gerne behilflich. Kontaktieren Sie uns dazu einfach unter support@evision-systems.de und wir setzen uns mit Ihnen in Verbindung.

Mehr zu den verschiedenen Eingabetools finden sie auf unser HDL Design Seite.

Verifizieren des HDL Codes in der Hardwareentwicklung

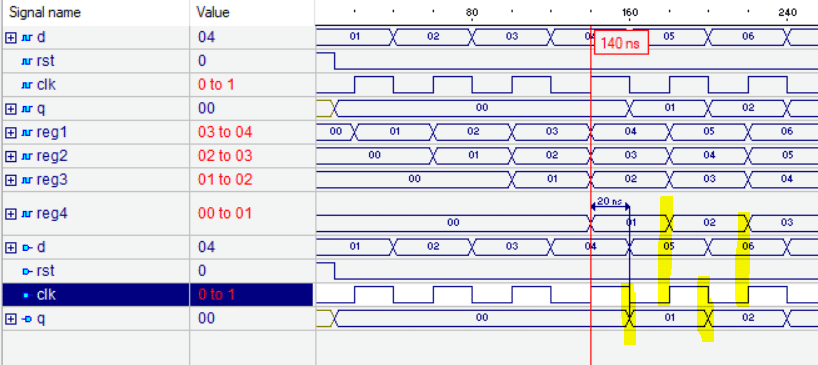

Um Fehler im Design rechtzeitig zu finden, gibt es verschiedene Verifikationsmethoden. Als erstes kann man mit statischen Verfahren feststellen, ob der Code hinsichtlich Syntax und Semantik richtig geschrieben ist und ob es strukturelle Probleme innerhalb des Codes gibt. Hier kann man aber in der Regel keine funktionalen Aspekte berücksichtigen.