eVision Systems GmbH, Forstinning – 18. Oktober 2019 – Aldec, Inc., ein führender Anbieter für gemischte HDL- Sprachsimulation und Hardware-unterstützte Verifikation für ASIC- und FPGA-Design, stellt auf der DVCon Europe (29. – 30. Oktober, München, Deutschland) aus und präsentiert eine leistungsfähige Hybrid Co-Emulations-Plattform für umfangreiche ASIC- und SOC-Designs.

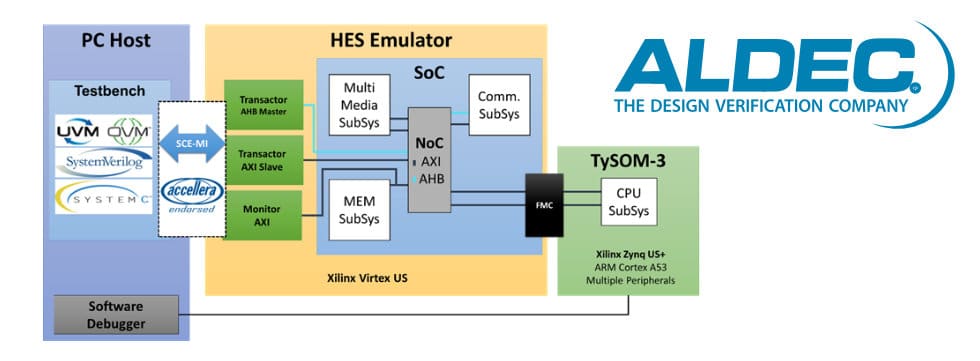

Die Plattform wurde unter Einbindung eines Aldec HES-US-440 Hardware-Emulationssystems und eines Aldec TySOM-3 Embedded System Boards erstellt, wobei der letztgenannte ein Xilinx Zynq® Ultrascale+TM FPGA bietet, das einen Quad-Core ARM® Cortex-A53 enthält. Eine FMC Host2Host- Brücke zwischen den beiden Aldec-Produkten ermöglicht es mittels TySOM-Board, die ARM-Kerne mit HES (Hardware Embedded Simulation) zu teilen, so dass die Mitglieder des Softwareteams auf einer Hardware mit schneller Taktrate Prototypen erstellen können und von einem schnellen Systemstart (Minuten statt Stunden) profitieren.

Aldec zeigt außerdem die kürzlich eingeführte automatische FPGA-Partitionierungsfunktion seines bekannten HES-DVMTM Tools; der vollständig automatisierten und skalierbaren Hybrid- Verifikationsumgebung des Unternehmens für SoC- und ASIC-Designs. Üblicherweise und abhängig von der Komplexität und den Einschränkungen eines Designs kann die manuelle Partitionierung mehrerer FPGAs für die Erstellung von Prototypen Tage oder sogar Wochen in Anspruch nehmen, wohingegen HES- DVM die Aufgabe in Minuten erledigen kann.

„Wir stellen auf der DVCon Europe Lösungen vor, die das veranschaulichen, worum es im Bereich der Electronic Design Automation (EDA) geht: Das enorme Einsparen von Entwicklungszeit und die Verbesserung von Sicherheit in der Verification durch Automation.“, kommentiert Krzysztof (Chris) Szczur, ein Aldec Hardware Verification Products Manager, der an beiden Tag an Stand Nr. 405 auf der DVCon Europe vertreten sein wird.

Außerdem wird Aldec die DVCon Europe nutzen, um die neuesten Funktion in Active-HDLTM vorzustellen, der auf Windows® basierenden, integrierten Erstellungs- und Simulationslösung für FPGA-Design, die eine komplett integrierte HDL Entwicklungsumgebung bestehend aus textbasierender und grafischer Eingabe die nahtlos mit den Simulator integriert sind und alle Sprachen auf RTL und Gate Level unterstützt.

Aldec wird zudem eine Vorschau auf zahlreiche Funktionen liefern, die für die Integration in die nächste Version von Riviera-PROTM geplant sind, der bekannten Verifikationsplattform des Unternehmens, die Support für die neuesten Verifikationsbibliotheken (z. B. von UVM) bietet, sowie Algorithmen für die Simulationsoptimierung, um optimale Leistung in VHDL, Verilog, SystemVerilog, SystemC und gemischtsprachige Simulationen zu erzielen.

Preise und Verfügbarkeit

Informationen zu Preisen und Verfügbarkeit sind unter diesem Kontakt erhältlich:

Email:sales@evision-systems.de

Pressekontakt:

eVision Systems

Jahnstr. 12

D – 85661 Forstinning b. München

Josef Ostermeier

Tel : 08121-220825