Agnisys hat seinen ursprünglichen Fokus von der Registerautomatisierung auf spezifikationsgesteuertes Design, Verifikation, Embedded-Programmierung, Validierung und Dokumentation von IPs und SoCs erweitert. Diese Erweiterung ist sowohl ein Beweis für das Wachstum von Agnisys als Unternehmen als auch für die vielen Herausforderungen, denen sich Halbleiter-Entwicklungsteams stellen müssen. Die schiere Komplexität ist das offensichtlichste Problem; die heutigen Designs enthalten Milliarden von Gattern mit Tausenden von Blöcken und unzähligen Verbindungen.

Es ist unmöglich, einen so großen Chip ohne effektive Wiederverwendung zu entwickeln. Dies geschieht branchenweit über Standards, projektübergreifend mit Design- und Verifikations-IP und über verschiedene Ebenen hinweg, vom Block über das Subsystem bis hin zum kompletten SoC. Natürlich enthält jeder Chip auch neue Designinhalte, und die manuelle Erstellung des gesamten Designs, der Verifizierung und der Software kostet wertvolle Zeit und verbraucht wertvolle Ressourcen. Enge Projektzeitpläne verlangen, dass die Codegenerierung so weit wie möglich automatisiert wird, wodurch auch manuelle Kodierungsfehler minimiert und die Codequalität verbessert werden.

Die Herausforderungen sind bei einem SoC aufgrund der Kombination von Hardware und Software größer als bei einem herkömmlichen Chip. Die Designblöcke müssen richtig integriert werden, die eingebettete Software, die diese Blöcke steuert, muss zusammengeführt werden, und das gesamte Hardware-Software-System muss gemeinsam validiert werden. Außerdem sind mehrere Ingenieure beteiligt: Teams für Architektur, Hardware-Design, Verifizierung, eingebettete Programmierung und System-Validierung. Eine gemeinsame Spezifikation ist unerlässlich, damit diese Teams zusammenarbeiten können, aber das ist leichter gesagt als getan. Es gibt keine Standardmethode zur Erfassung von Spezifikationen, und verschiedene Teams verwenden unterschiedliche Methoden. Die meisten verwenden natürliche Sprache, die von Natur aus mehrdeutig ist und unterschiedliche Interpretationen zulässt.

Selbst wenn es eine perfekte Spezifikation gibt, ist der Wandel die einzige Gewissheit. Probleme, die während der Implementierung entdeckt werden, und Reaktionen auf den Wettbewerbsdruck machen es erforderlich, jede Spezifikation bei jedem Projekt mehrmals zu ändern. Wann immer dies geschieht, führt es zu einem Wasserfall-Effekt. Änderungen am Hardware-Design sind fast immer notwendig und erfordern eine erneute Überprüfung. In vielen Fällen sind auch Software-Revisionen erforderlich, die eine erneute Validierung verlangen. Die Dokumentation für den Endbenutzer muss an die geänderte Spezifikation angepasst werden. Wenn alle Aktualisierungen für das Design, die Verifizierungsumgebung, den eingebetteten Code und die Dokumentation mehrmals pro Projekt manuell vorgenommen werden, sind die Auswirkungen enorm.

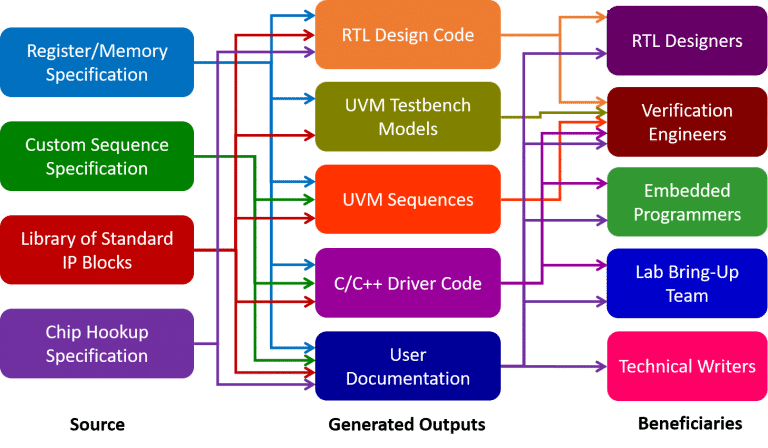

Eine spezifikationsgesteuerte Automatisierung ist die einzige praktikable Lösung. Wann immer möglich, müssen Spezifikationen in einem ausführbaren Format erfasst und zur automatischen Generierung von Code und Dokumentation für alle Phasen des Entwicklungsprozesses verwendet werden. Hier kommt Agnisys ins Spiel. Wir bieten eine breite Palette von Produkten an, die viele Spezifikationsformen unterstützen, auf Korrektheit prüfen und dann die Generierungsschritte durchführen. Wie das folgende Diagramm zeigt, bietet dieser Prozess Vorteile für mehrere Teams in einem IP- oder SoC-Projekt.

Dieser Prozess hat vier primäre Spezifikationen:

Spezifikation für Register und Speicher

Die Spezifikation für Register und Speicher wird verwendet, um RTL-Code für das Design, UVM-Testbench-Modelle und Sequenzen für die Verifizierung, C/C++-Code für Treiber und eingebettete Software sowie Benutzerdokumentation zu erzeugen.

Standard-IP-Blöcke

Für Standard-IP-Blöcke generiert die Bibliothek alle dieselben Ausgaben.

Benutzerdefinierte Sequenzen

Für Nicht-Standardblöcke erzeugt die Spezifikation für benutzerdefinierte Sequenzen UVM-Sequenzen, C/C++-Code und Dokumentation.

Chip-Hookup-Spezifikation

Für die Verbindung von IP- und benutzerdefinierten Blöcken auf SoC-Ebene generiert die Chip-Hookup-Spezifikation das Top-Level-RTL-Design und die Dokumentation.

Von diesem Prozess profitieren fünf primäre Projektteams:

- Die Hardware-Designer verwenden den generierten RTL-Code als Teil ihrer Designs.

- Das Verifikationsteam bindet die generierten UVM-Modelle und -Sequenzen in seine Testbenches ein und kann den generierten C/C++-Code auch zur anfänglichen Validierung ausführen

- Die Embedded-Programmierer integrieren den generierten C/C++-Code in ihre Treiber und andere Software, die direkt mit der Hardware kommuniziert.

- Das Inbetriebnahmeteam führt die Treiber und den eingebetteten Code im Labor als Teil der Validierung der Hardware und Software des gesamten Systems aus.

- Die technischen Redakteure binden die generierte Dokumentation in ihre Benutzerhandbücher ein.

Da sich die Spezifikationen häufig ändern, spart dieser Prozess nicht nur einmal, sondern viele Male während des Projekts Zeit und Ressourcen. Handkodierung, mühsame manuelle Aktualisierungen, eingeführte Fehler und der Verifizierungsaufwand, um sie zu finden und zu beheben, entfallen. Agnisys automatisiert Hardware-Design, Software-Codierung, Verifizierung, Validierung und Dokumentation für viele Bereiche der IP- und SoC-Entwicklung. Um mehr darüber zu erfahren, wie dieser Prozess funktioniert und welche Produkte welche Aspekte des Ablaufs abdecken, sehen Sie sich bitte das Agnisys DVCon-Einführungsvideo an.

Sie sehen gerade einen Platzhalterinhalt von Standard. Um auf den eigentlichen Inhalt zuzugreifen, klicken Sie auf den Button unten. Bitte beachten Sie, dass dabei Daten an Drittanbieter weitergegeben werden.

Weitere InformationenSpezifikationsautomatisierung für Entwickler

Anforderungen für verschiedene Projektteams und verschiedene Aufgaben im System-on-Chip (SoC)-Entwicklungsprozess: Hardware-Design, Simulation, formale Verifizierung, Firmware-Codierung, Validierung auf Systemebene und mehr.

Ein hoher Qualitätsstandard für standardbasiertes IP

Die Standard Library of IP Generators (SLIP-G™) hat sich bei den Anwendern als sehr beliebt erwiesen, und das ist nicht überraschend. Die Wiederverwendung spielt bei der Entwicklung von System-on-Chip (SoC) eine große Rolle.

Automatisierung des UVM Register Abstraction Layers (RAL)

Dieser Beitrag konzentriert sich auf den UVM Register Abstraction Layer (RAL), auch UVM Register Layer genannt. Die heutigen großen System-on-Chip (SoC)-Entwürfe enthalten viele Steuer- und Statusregister, auf die oft sowohl von eingebetteter Software oder Treibern als auch von der Hardware aus zugegriffen werden kann

Englische Beschreibung automatisch in SystemVerilog Assertions übersetzen

Agnisys hat einen einzigartigen Ansatz entwickelt, bei dem künstliche Intelligenz (KI) und maschinelles Lernen (ML) eingesetzt werden, um englische Beschreibungen der Entwurfsabsicht in SystemVerilog Assertions (SVA) zu übersetzen.

Ein einheitlicher Entwicklungsablauf für embedded Systeme

Agnisys hat einen einheitlichen Entwicklungsablauf für Embedded Systems definiert, der alles miteinander verzahnt. Sie bieten eine Methodik und Richtlinien dafür, wie und wann die einzelnen Werkzeuge eingesetzt werden, um den größten Nutzeffekt zu erzielen.