Die Standard Library of IP Generators (SLIP-G™) hat sich bei den Anwendern als sehr beliebt erwiesen, und das ist nicht überraschend. Die Wiederverwendung spielt bei der Entwicklung von System-on-Chip (SoC) eine große Rolle, da es sich kein Team leisten kann, eine Milliarde oder mehr Gatter von Grund auf zu entwerfen und zu verifizieren. Es besteht keine Aussicht auf eine Umkehrung dieses Trends, daher sehen wir ein großes Interesse an vielen Arten von Design- und Verifikations-IP’s, insbesondere an solchen, die Industriestandards implementieren. Agnisys hat intensiv daran gearbeitet, die Anwender zu unterstützen und deren IP-Titel zu erweitern.

Es ist wichtig zu betonen, dass Agnisys eine Bibliothek von IP-Generatoren und keine festen IP-Blöcke anbietet. Dies ist angesichts der Vielfalt der Anwendungen, die SoCs verwenden, sowie der Mischung von Technologien (FPGA, ASIC und vollständig kundenspezifisch), die für den Aufbau dieser komplexen Chips verwendet werden, von wesentlicher Bedeutung. Jedes Chip-Projekt hat seine eigenen Anforderungen an seine IP-Blöcke, wobei sich die Auswahl der Funktionen oft aus Kompromissen zwischen Geschwindigkeit, Fläche und Leistung ergibt. Nur eine generationenabhängige Lösung kann diese Anforderungen erfüllen. Optionen und Anpassungen müssen in die Generatoren eingebaut werden, damit die Anwender nicht in Versuchung kommen, die Register-Transfer-Level (RTL)-Designdateien manuell zu bearbeiten.

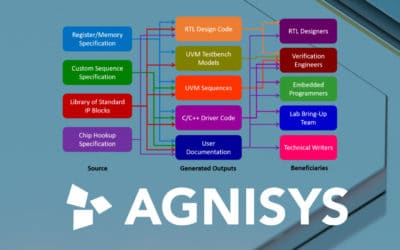

SLIP-G generiert den IP-RTL-Code, der zusammen mit den Teilen des Designs des Anwenders in das vollständige SoC integriert wird. Agnisys SoC Enterprise™ (SoC-E) automatisiert diesen Prozess und arbeitet nahtlos mit SLIP-G zusammen. Agnisys bietet jedoch viel mehr als nur das Design. Für jede IP generiert SLIP-G auch UVM-Modelle (Universal Verification Methodology), die bei der Erstellung der Verifikationstestbench helfen, sowie eine Reihe von Programmiersequenzen zur Initialisierung und Konfiguration der Register des ausgewählten Blocks. Darüber hinaus generieren Sie C/C++-Sequenz-APIs (Application Programming Interfaces) für die Entwicklung von Firmware und Treibern, die auf den IP-Block zugreifen.

Schließlich erstellt Agnisys eine Dokumentation, die so ausführlich ist, dass sie den Endbenutzern des SoCs zur Verfügung gestellt werden kann. SLIP-G hilft jeder Gruppe, die an der SoC-Entwicklung beteiligt ist: Hardware-Designer, Verifizierungsteam, Labor-Ingenieure für die Inbetriebnahme/Validierung und technische Redakteure. Agnisys stellt sogar Ausgabedateien zur Verfügung, die bei der Entwicklung von Programmen für automatisierte Testgeräte (ATE) für Produktions-Chips im Herstellungsprozess verwendet werden können. Dabei setzt Agnisys einen hohen Standard für die Bereitstellung von standardbasiertem geistigem Eigentum, und während die Bibliothek erweitert wird, bieten Agnisys weiterhin die gleiche Qualität und Flexibilität für alle neuen Titel.

SLIP-G wurde letztes Jahr mit vier IP-Blöcken eingeführt: General Purpose Input/Output (GPIO), I2C, Timer und Programmable Interrupt Controller (PIC). Diese haben viele Konfigurations- und Anpassungsoptionen, um die Anforderungen einer vielfältigen Benutzerbasis zu erfüllen. In diesem Jahr wurden bisher vier weitere Einträge in die Bibliothek aufgenommen: Direct Memory Access (DMA), Serial Peripheral Interface (SPI), Pulse Width Modulation (PWM) und Advanced Encryption Standard (AES). Dies sind zahlreiche Optionen, die bei der Generierung dieser Blöcke mit SLIP-G zur Verfügung stehen.

Das DMA ermöglicht SoC-Subsystemen den Zugriff auf den Hauptspeicher des Systems unabhängig von der Zentraleinheit (CPU). Dadurch wird die CPU für wichtige Berechnungen freigestellt, anstatt einfach nur Daten zu verschieben. Die DMA-IP hat zwei Master und vier Kanäle mit integrierter Round-Robin-Arbitrierung über die Kanäle hinweg. Sie kann Übertragungen von Speicher zu Peripherie, Peripherie zu Speicher, Peripherie zu Peripherie und Speicher zu Speicher verarbeiten. Es bietet eine konfigurierbare Anzahl von Kanälen und umfasst einen Interrupt-Controller für Status und Diagnose.

SPI ist eine synchrone serielle Schnittstellenspezifikation, die für die Kommunikation über kurze Strecken verwendet wird. Die CPU verwendet die SPI-Register zur Programmierung des IP-Blocks, um eine Transaktion zu initiieren. Die Datenlänge, die Befehlslänge und die Adresslänge sind alle konfigurierbar. Zu den Optionen gehört auch, ob Interrupts mit einer Freigabe oder einer Maske erzeugt werden sollen. PWM ist eine Methode zur Steuerung analoger Geräte mit einem digitalen Ausgang durch Modulation eines Ausgangssignals. Es ist eines der wichtigsten Mittel, mit dem Prozessoren analoge Geräte wie Motoren mit variabler Geschwindigkeit, dimmbare Lichter, Aktuatoren und Lautsprecher steuern. Der PWM-IP-Block bietet folgende Merkmale:

- Anpassbare Anzahl von PWM-Ausgangssignalen

- Anpassbare Anzahl von externen Quellen

- Ein Prescaler-Register zur Erzeugung der PWM-Signale mit einem langsameren Takt als dem Systemtakt

- Anpassbare Breiten für Steuerregister

- Standard-APIs zur Programmierung des Blocks

AES ist ein Standard zur Ver- und Entschlüsselung sensibler elektronischer Daten, der sowohl auf Hardware als auch auf Software anwendbar ist. Er kann drei verschiedene Schlüsselgrößen (128, 192 und 256 Bit) verarbeiten und unterstützt eine Blockgröße von 128 Bit. Wir unterstützen 128-Bit-Schlüssel und 128-Bit-Blöcke. Bei der IP-Generierung kann der Benutzer wählen, ob der Schlüsselwert dem Block über ein Eingangssignal zugeführt oder im RTL-Code definiert werden soll. In letzterem Fall gibt der Benutzer den Schlüsselwert an. Zu den weiteren Anpassungsoptionen gehört, ob der Block für Verschlüsselung oder Entschlüsselung konfiguriert wird.

SLIP-G ermöglicht auch die Anpassung durch den Benutzer, z. B. das Hinzufügen von Feldern zu vorhandenen Registern, das Hinzufügen zusätzlicher Register, das Hinzufügen von Logik zur IP und das Einrichten von Abhängigkeiten von Ereignissen innerhalb des IP-Blocks. Agnisys fügt laufend neue Generierungsoptionen auf der Grundlage von Benutzeranfragen hinzu und baut die Bibliothek weiter aus. Agnisys is auch vor kurzem der Mobile Industry Processor Interface (MIPI) Alliance beigetreten und erwägt die Entwicklung von MIPI-basierter IP’s. Deren Standards erstrecken sich auf Kamera, Displays, Energieverwaltung und vieles mehr, so dass Agnisys davon ausgeht, dass es ein erhebliches Interesse bei der Benutzerbasis geben wird.

Bitte lassen Sie uns wissen, wenn Sie Vorschläge für neue IP-Titel oder neue Funktionen für bestehende Blöcke haben. Agnisys ist stolz auf ihre SLIP-G-Familie und die einzigartige Unterstützung für die Wiederverwendung von Hardware, die Wiederverwendung von Verifikationsdaten, die Wiederverwendung von Programmiersequenzen und die Wiederverwendung von Dokumentation. Agnisys freut sich Sie bei der Entwicklung immer größerer SoCs unterstützen zu können und das ohne die Größe Ihres Teams oder Ihre Projektzeitpläne explodieren.

Spezifikationsautomatisierung für Entwickler

Anforderungen für verschiedene Projektteams und verschiedene Aufgaben im System-on-Chip (SoC)-Entwicklungsprozess: Hardware-Design, Simulation, formale Verifizierung, Firmware-Codierung, Validierung auf Systemebene und mehr.

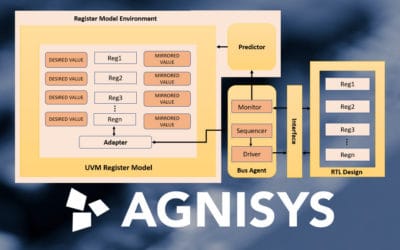

Automatisierung des UVM Register Abstraction Layers (RAL)

Dieser Beitrag konzentriert sich auf den UVM Register Abstraction Layer (RAL), auch UVM Register Layer genannt. Die heutigen großen System-on-Chip (SoC)-Entwürfe enthalten viele Steuer- und Statusregister, auf die oft sowohl von eingebetteter Software oder Treibern als auch von der Hardware aus zugegriffen werden kann

Automatisierung der IP- und SoC-Entwicklung

Agnisys hat seinen ursprünglichen Fokus von der Registerautomatisierung auf spezifikationsgesteuertes Design, Verifikation, Embedded-Programmierung, Validierung und Dokumentation von IPs und SoCs erweitert. Diese Erweiterung ist sowohl ein Beweis für das Wachstum von Agnisys als Unternehmen als auch für die vielen Herausforderungen, denen sich Halbleiter-Entwicklungsteams stellen müssen

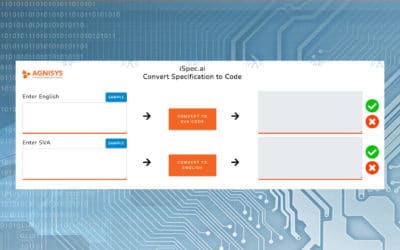

Englische Beschreibung automatisch in SystemVerilog Assertions übersetzen

Agnisys hat einen einzigartigen Ansatz entwickelt, bei dem künstliche Intelligenz (KI) und maschinelles Lernen (ML) eingesetzt werden, um englische Beschreibungen der Entwurfsabsicht in SystemVerilog Assertions (SVA) zu übersetzen.

Ein einheitlicher Entwicklungsablauf für embedded Systeme

Agnisys hat einen einheitlichen Entwicklungsablauf für Embedded Systems definiert, der alles miteinander verzahnt. Sie bieten eine Methodik und Richtlinien dafür, wie und wann die einzelnen Werkzeuge eingesetzt werden, um den größten Nutzeffekt zu erzielen.