Es gibt unterschiedliche Anforderungen für die verschiedenen Projektteams und Aufgaben im System-on-Chip (SoC)-Entwicklungsprozess: Hardware-Design, Simulation, formale Verifizierung, Firmware-Codierung, Validierung auf Systemebene und mehr. Der Schwerpunkt liegt dabei nicht so sehr auf einzelnen Produkten, sondern vielmehr darauf, wie sie zusammenarbeiten, um mehrere Phasen des Prozesses anhand ausführbarer Spezifikationen zu automatisieren.

Die relativ neue Lösung IDS NextGen (IDS-NG™), bietet ein gemeinsames Frontend und „Dashboard“ für alle Benutzer in den verschiedenen Teams.

In dem Webinar „IDS-NG for Design„, wurde dies aufgezeigt. Agnisys hat einige der Probleme skizziert, mit denen Chipdesigner heute konfrontiert sind, und verschiedene Möglichkeiten aufgezeigt, wie die Lösung von Agnisys zur Automatisierung von Spezifikationen helfen kann. Zu diesen Herausforderungen gehören:

- Entwurf großer, komplexer Sätze von Steuer- und Statusregistern

- Ordnungsgemäße Handhabung von Taktbereichsüberschneidungen

- Beschaffung von robuster, aber flexibler IP für standardbasierte Blöcke

- Unterstützung von komplexen Busprotokollen

- Zusammenschaltung von IPs und kundenspezifischen Blöcken

- Erfüllung von Anforderungen an funktionale Sicherheit und Security

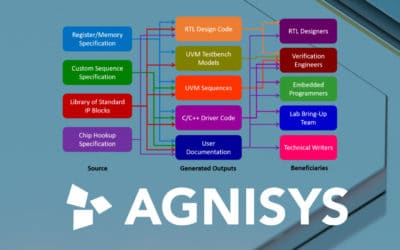

Agnisys generiert das komplette RTL-Design für die angegebenen Register und entlasten das Designteam vor allen mit den verbundenen Codierungsarbeiten. Agnisys macht die Designer bei den anderen Projektteams beliebt, da Sie auch UVM-Modelle (Universal Verification Methodology) für die Verifikationsingenieure, C/C++-Header für die Embedded-Programmierer und Dokumentation für die technischen Redakteure generieren. Dadurch werden Fehler vermieden, die auf unterschiedliche Interpretationen der Spezifikation oder auf die Verwendung unterschiedlicher Versionen der Spezifikation zurückzuführen sind. Jede Änderung der Spezifikation führt zu einer Neugenerierung für alle Teams, so dass sie auf dem gleichen Stand bleiben.

Agnisys generiert auch den RTL-Code, der notwendig ist, um Metastabilität und andere Probleme beim clock domain crossings (CDCs) zu vermeiden. Bei der Erstellung der Register erkennt IDS-NG, wenn sie sich in einer anderen Taktdomäne befinden als der Systembus oder wenn sie sich in einer eindeutigen Taktdomäne befinden, die sich vom Systembus und dem Rest des Hardwaredesigns unterscheidet. Agnisys unterstützt mehrere bewährte Arten der Synchronisation über die CDC-Grenze hinweg, darunter Flip-Flop auf zwei Ebenen, Multiplexer und Handshake. Außerdem unterstützet die Software das Verifizierungsteam, indem die relevanten Assertions für die formale CDC-Analyse generiert werden.

Im letzten Blogbeitrag wurde die Herausforderungen von standardbasierter IP erörtert und Agnisys SLIP-G™-Bibliothek von IP-Generatoren vorgestellt. Entwickler haben viele Möglichkeiten, die von Agnisys generierten IP-Blöcke zu konfigurieren und anzupassen. Zu den derzeit unterstützten Standards gehören General Purpose Input/Output (GPIO), I2C, Timer, Programmable Interrupt Controller (PIC), Direct Memory Access (DMA), Serial Peripheral Interface (SPI), Pulse Width Modulation (PWM) und Advanced Encryption Standard (AES). In allen Fällen wird das RTL-Design, UVM-Modelle, Programmiersequenzen und die Dokumentation erstellt.

Ein typisches SoC besteht aus vielen tausend Blöcken, von denen einige auf Standards basieren, andere von anderen Quellen lizenziert sind und wieder andere kundenspezifisch entwickelt wurden. Das Zusammenfügen all dieser Blöcke zum Top-Level-Chip ist eine große und ziemlich mühsame Aufgabe. Glücklicherweise automatisiert IDS-NG auch diesen Prozess für Sie. Wie zu erwarten, generieren Agnisys den gesamten RTL-Code, der für die Verbindung der Blöcke aus SLIP-G erforderlich ist. Sie können auch angeben, wie benutzerdefinierte Blöcke integriert werden sollen, und generieren auch diesen Teil des RTL-Designs. Schließlich werden nach Bedarf RTL-Aggregatoren, Brücken und Multiplexer für Standardbusse generiert.

Ein hoher Qualitätsstandard für standardbasiertes IP

Die Standard Library of IP Generators (SLIP-G™) hat sich bei den Anwendern als sehr beliebt erwiesen, und das ist nicht überraschend. Die Wiederverwendung spielt bei der Entwicklung von System-on-Chip (SoC) eine große Rolle.

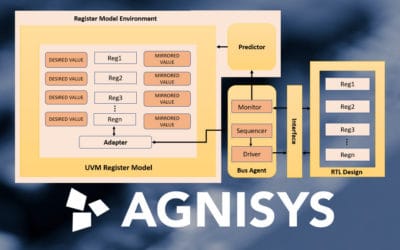

Automatisierung des UVM Register Abstraction Layers (RAL)

Dieser Beitrag konzentriert sich auf den UVM Register Abstraction Layer (RAL), auch UVM Register Layer genannt. Die heutigen großen System-on-Chip (SoC)-Entwürfe enthalten viele Steuer- und Statusregister, auf die oft sowohl von eingebetteter Software oder Treibern als auch von der Hardware aus zugegriffen werden kann

Automatisierung der IP- und SoC-Entwicklung

Agnisys hat seinen ursprünglichen Fokus von der Registerautomatisierung auf spezifikationsgesteuertes Design, Verifikation, Embedded-Programmierung, Validierung und Dokumentation von IPs und SoCs erweitert. Diese Erweiterung ist sowohl ein Beweis für das Wachstum von Agnisys als Unternehmen als auch für die vielen Herausforderungen, denen sich Halbleiter-Entwicklungsteams stellen müssen

Webinar zur Embedded Systementwicklung mit Agnisys

Die Agnisys-Methode zur Entwicklung von Embedded-Produkten. Auf diese Weise lassen sich viele Fallstricke vermeiden, die in einem typischen Workflow auftreten, wie z. B. ein langsamer Prozess, doppelter Aufwand, verschwenderische Ressourcen usw.

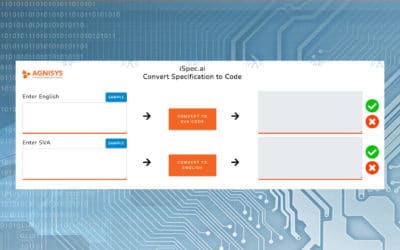

Englische Beschreibung automatisch in SystemVerilog Assertions übersetzen

Agnisys hat einen einzigartigen Ansatz entwickelt, bei dem künstliche Intelligenz (KI) und maschinelles Lernen (ML) eingesetzt werden, um englische Beschreibungen der Entwurfsabsicht in SystemVerilog Assertions (SVA) zu übersetzen.

Ein einheitlicher Entwicklungsablauf für embedded Systeme

Agnisys hat einen einheitlichen Entwicklungsablauf für Embedded Systems definiert, der alles miteinander verzahnt. Sie bieten eine Methodik und Richtlinien dafür, wie und wann die einzelnen Werkzeuge eingesetzt werden, um den größten Nutzeffekt zu erzielen.