Die Open Verification Library (OVL) ist eine Bibliothek von Property Checkern für digitale Schaltkreisbeschreibungen, die in gängigen Hardware Description Languages geschrieben sind und von Accelera gepflegt werden. Die OVL Checker können nicht nur in der dynamischen Simulation, sondern auch in der formalen Verifikation und Emulation eingesetzt werden. Außerdem bietet die OVL-basierte Verifikationstechnologie den Entwicklern die einfachste Möglichkeit, eine Assertion-basierte Verifikation ihres Designs zu implementieren. Schließlich unterstützt OVL jede HDL-Sprache (Verilog, SystemVerilog, VHDL) und ermöglicht so eine Assertion-basierte Verifikation mit jedem Simulationswerkzeug.

In diesem Webinar werden wir praktische Anleitungen für den Einsatz der Open Verification Library (OVL) im Design- und Verifikationsprozess vorstellen. Anhand verschiedener Codebeispiele wird gezeigt, wie OVL effizient für die Verifikation von Verilog- und VHDL-Designs eingesetzt werden kann. Statische, formale und emulationsbasierte Verifikationsmethoden, die OVL verwenden, werden ebenfalls vorgestellt.

Agenda:

- Assertion-basierte Verifikation: Ein Überblick

- Einführung in die Assertion-Based Verification mit OVL

- Anwendung der OVL-basierten Verifikation auf HDL-Designs

- Verwendung von OVL-Checkern bei Emulation/Prototyping

- Formale Modellprüfung mit OVL

- Live-Demo

Wesentliche Schritte zur Vereinfachung von VHDL-Testbenches mit OSVVM

Dieses Webinar zum Thema „Erste Schritte“ konzentriert sich auf die ersten, wesentlichen Schritte, die Sie unternehmen müssen, wenn Sie Ihren VHDL-Testbench-Ansatz mit OSVVM verbessern wollen.

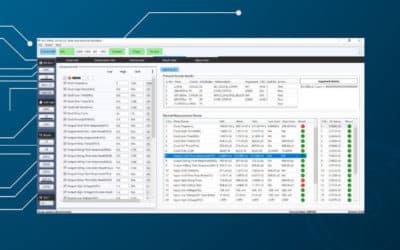

Überprüfung von AXI-Verbindungen mit ALINT-PRO und Riviera-PRO

AXI ist das beliebteste interne Busprotokoll bei den heutigen FPGA- und SoC-FPGA-Designs geworden. Mit ALINT-PRO können FPGA-Designer AXI-Busschnittstellen extrahieren, überprüfen und statisch verifizieren. Darüber hinaus kann ALINT-PRO bei der automatischen...

SHA850A – Neuer Spektrum- und Vektornetzwerkanalysator

Der neue Analysator ist hochintegriert und speziell für den Feldbetrieb konzipiert. Das Gerät ist handlich und leicht und hat viele nützliche Analysefunktionen integriert.

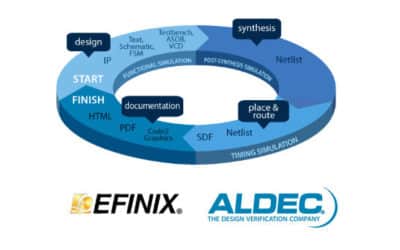

Effinix und Aldec Active-HDL Promoaktion

Active-HDL Designer Edition Perpetual Lizenz – Fordern Sie ein Angebot an! Active-HDL™ ist eine Windows®-basierte, integrierte FPGA-Design-Erstellungs- und Simulationslösung für teambasierte Entwicklungsumgebungen.

embedded world 2023

Vom 14. bis 16. März steht die embedded world in Nürnberg wieder für Besucher offen. Am Stand 4-548 von eVision Systems freuen wir uns auf alle, die unsere vielen neuen Innovationen kennenlernen möchten!

Branchenweit erste elektrische AC DC Validierungslösung für SD-Karten und eMMC-Geräte

PGY-SSM-EV-TesterForstinning (Deutschland), 23. November 2022 - eVision Systems GmbH, autorisierter Distributor von Prodigy Technovations für Zentraleuropa, kündigt den SD, eMMC AC/DC Electrical Validation Tester (PGY-SSM-EV-Tester) für die elektrische Überprüfung von...